# **HMPI: A Message-Passing Library for Heterogeneous Networks of Computers**

**Manumachu Ravi Reddy**

**Doctor of Philosophy Dissertation**

**June 2005**

**Head of Department: Barry Smyth

Supervisor: Alexey Lastovetsky**

**Computer Science Department,

University College Dublin,

Belfield,

Dublin.**

*To my parents...*

*Manumachu Sree Rami Reddy*

*Manumachu Koteswari*

## **Acknowledgements**

During the course of this research, I have had great privilege to work with a very competent group of people. I would like to take this opportunity to thank every one of them.

I would like to thank my supervisor, Alexey Lastovetsky, for being available at all times to offer valuable advice and guidance. I'm very happy to have continued my collaboration with Alexey from industry into academia. We have had many insightful discussions, which have greatly helped me getting to understand the nitty-gritty of the area of heterogeneous computing. I'm grateful to Alexey Kalinov and Neil Hurley for providing valuable feedback on my dissertation. I would like to acknowledge the useful review comments provided by Jack Dongarra on the design of the interfaces in my research work.

I'm greatly indebted to the staff and postgraduates of the computer science department. I'm very grateful to Gerry Dunnion for providing and administering the computing resources to run my parallel experiments. I appreciate all the assistance provided by Patricia Geoghegan in dealing with the administrative formalities. I would like to thank the members of the postgraduate soccer team for all the laughs on and off the soccer pitch.

I would like to thank my friends -- Abhay, Leena, Bart, Narinder, Pramilla, Victor, Ajit, Rahul, Pracchi, Anirudh, Andy, Viv and Jeff -- for keeping me motivated through this arduous but exciting journey. I would specially like to thank Srinivas Chillara for taking time out to proofread and review this dissertation and Hanumantha Rao for giving words of wisdom related to the research experience.

And finally, I would like to thank my parents, who throughout my life have always been there to give me encouragement and support.

## Table of Contents

|          |                                                                                                |           |

|----------|------------------------------------------------------------------------------------------------|-----------|

| <b>1</b> | <b>Introduction .....</b>                                                                      | <b>1</b>  |

| <b>2</b> | <b>Related Work .....</b>                                                                      | <b>9</b>  |

| 2.1      | <i>High-level Parallel Programming Tools .....</i>                                             | 10        |

| 2.1.1    | <i>Summary .....</i>                                                                           | 17        |

| 2.2      | <i>MPI Extensions/Implementations for HNOCs .....</i>                                          | 18        |

| 2.2.1    | <i>Summary .....</i>                                                                           | 20        |

| 2.3      | <i>Data Partitioning .....</i>                                                                 | 21        |

| 2.3.1    | <i>Summary .....</i>                                                                           | 38        |

| 2.4      | <i>Performance Models of Parallel Computers .....</i>                                          | 39        |

| 2.4.1    | <i>Summary .....</i>                                                                           | 47        |

| 2.5      | <i>Static and Dynamic Mapping Strategies .....</i>                                             | 48        |

| 2.5.1    | <i>Summary .....</i>                                                                           | 61        |

| 2.6      | <i>High-Performance Computing on Global Networks .....</i>                                     | 62        |

| 2.7      | <i>Summary .....</i>                                                                           | 65        |

| <b>3</b> | <b>Outline of HMPI .....</b>                                                                   | <b>67</b> |

| 3.1      | <i>Outline of Performance Model Definition Language .....</i>                                  | 70        |

| 3.1.1    | <i>Homogeneous Distribution of Data with Heterogeneous<br/>Distribution of Processes .....</i> | 72        |

| 3.1.2    | <i>Main Constructs of Performance Model Definition Language ...</i>                            | 77        |

| 3.1.3    | <i>Structure of Target Program .....</i>                                                       | 88        |

| 3.2      | <i>HMPI Group Management Functions .....</i>                                                   | 98        |

| 3.2.1    | <i>Mapping Algorithm .....</i>                                                                 | 103       |

|          |                                                                                                             |            |

|----------|-------------------------------------------------------------------------------------------------------------|------------|

| 3.2.1.1  | <i>Model of a Heterogeneous Network of Computers</i> .....                                                  | 104        |

| 3.2.1.2  | <i>Overview of the Mapping Algorithm</i> .....                                                              | 108        |

| 3.3      | <i>Dynamic Updating of Processor Performances Using HMPI_Recon</i> .....                                    | 113        |

| 3.4      | <i>Estimation of Execution Time of an Algorithm using HMPI_Timeof</i> .....                                 | 115        |

| 3.5      | <i>Detection of Optimal Number of Processes using</i><br><i>HMPI_Group_auto_create</i> .....                | 122        |

| 3.5.1    | <i>Experimental Results using HMPI_Group_auto_create</i> .....                                              | 131        |

| 3.6      | <i>Model of HMPI Program</i> .....                                                                          | 156        |

| 3.7      | <i>Transformation of MPI to HMPI</i> .....                                                                  | 158        |

| 3.8      | <i>A Research Implementation of HMPI</i> .....                                                              | 165        |

| 3.8.1    | <i>Virtual parallel machine</i> .....                                                                       | 167        |

| 3.8.2    | <i>Model of HMPI program</i> .....                                                                          | 168        |

| 3.8.3    | <i>Structure of HMPI program</i> .....                                                                      | 172        |

| 3.9      | <i>Summary</i> .....                                                                                        | 175        |

| <b>4</b> | <b>The Heterogeneous Data Partitioning Interface (HDPI): Overview, Design and Preliminary Results</b> ..... | <b>178</b> |

| 4.1      | <i>A Realistic Performance Model of Networks of Heterogeneous Computers</i> .....                           | 182        |

| 4.1.1    | <i>Procedure for Building the Functional Performance Model</i> .....                                        | 191        |

| 4.1.1.1  | <i>Problem Formulation</i> .....                                                                            | 193        |

| 4.1.1.2  | <i>Load Functions</i> .....                                                                                 | 196        |

| 4.1.1.3  | <i>Assumptions</i> .....                                                                                    | 201        |

| 4.1.1.4  | <i>Definitions</i> .....                                                                                    | 203        |

| 4.1.1.5  | <i>Speed Function Approximation Building Procedure</i> .....                                                | 203        |

|                                                                        |                                                              |     |     |

|------------------------------------------------------------------------|--------------------------------------------------------------|-----|-----|

| 4.1.1.6                                                                | <i>Experimental Results</i> .....                            | 210 |     |

| 4.1.1.7                                                                | <i>Discussion and Future Work</i> .....                      | 213 |     |

| 4.2                                                                    | <i>Classification of Partitioning Problems</i> .....         | 215 |     |

| 4.3                                                                    | <i>Partitioning Problems for Sets and Ordered Sets</i> ..... | 216 |     |

| 4.4                                                                    | <i>Partitioning Problems for Dense Matrices</i> .....        | 225 |     |

| 4.5                                                                    | <i>Partitioning Problems for Graphs</i> .....                | 241 |     |

| 4.6                                                                    | <i>Partitioning Problems for Trees</i> .....                 | 251 |     |

| 4.7                                                                    | <i>Algorithms of Partitioning Sets</i> .....                 | 254 |     |

| 4.7.1 <i>Algorithms for Partitioning Sets without Processor Memory</i> |                                                              |     |     |

|                                                                        | <i>Bounds</i> .....                                          | 255 |     |

| 4.7.1.1 <i>Experimental Results</i> .....                              |                                                              |     | 272 |

|                                                                        | 4.7.1.1.1 <i>Applications</i> .....                          | 274 |     |

|                                                                        | 4.7.1.1.2 <i>Numerical Results</i> .....                     | 284 |     |

| 4.7.1.2 <i>Algorithms for Partitioning Sets with Processor Memory</i>  |                                                              |     |     |

|                                                                        | <i>Bounds</i> .....                                          | 288 |     |

| 4.7.2.1 <i>The Extended Performance Model of Networks of</i>           |                                                              |     |     |

|                                                                        | <i>Heterogeneous Computers</i> .....                         | 293 |     |

| 4.7.2.2 <i>Algorithm for Partitioning a Set with Processor Memory</i>  |                                                              |     |     |

|                                                                        | <i>Bounds</i> .....                                          | 294 |     |

| 4.7.2.3 <i>Applications of the Model</i> .....                         |                                                              |     | 300 |

| 4.7.2.4 <i>Experimental Results</i> .....                              |                                                              |     | 301 |

|                                                                        | 4.7.2.4.1 <i>Determination of Largest Problem Size</i> ....  | 301 |     |

|                                                                        | 4.7.2.4.2 <i>Applications</i> .....                          | 304 |     |

|                                                                                                                                   |                                                       |            |

|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------------|

| 4.7.2.4.3                                                                                                                         | <i>Numerical Results</i> .....                        | 306        |

| 4.7.2.5                                                                                                                           | <i>Related Work</i> .....                             | 308        |

| 4.8                                                                                                                               | <i>Summary</i> .....                                  | 312        |

| <b>5</b>                                                                                                                          | <b>HMPI Application Programming</b> .....             | <b>315</b> |

| 5.1                                                                                                                               | <i>Example of irregular HMPI application</i> .....    | 315        |

| 5.2                                                                                                                               | <i>Examples of regular HMPI application</i> .....     | 324        |

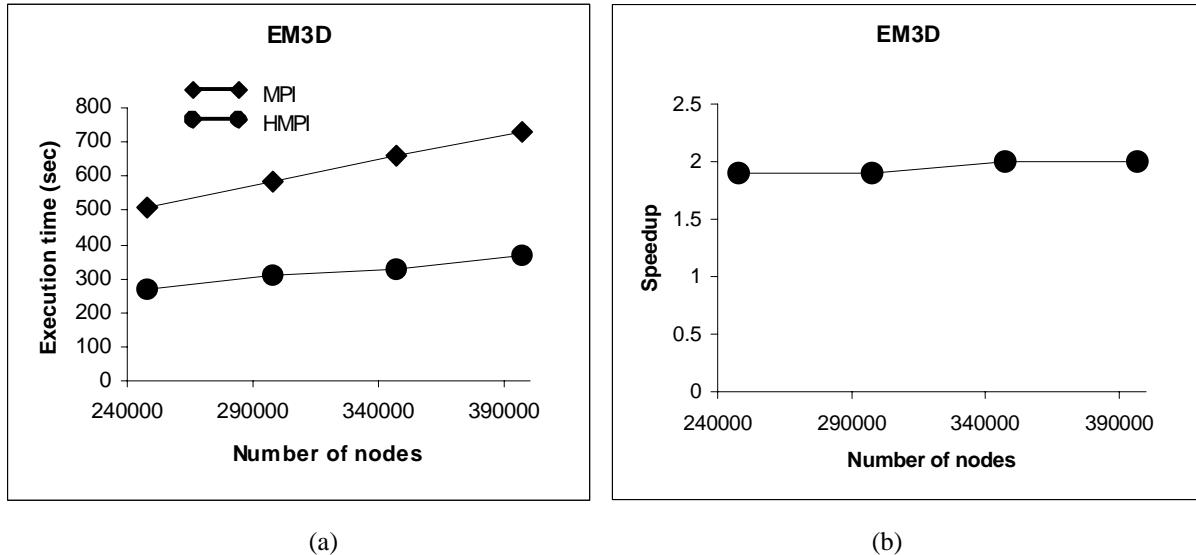

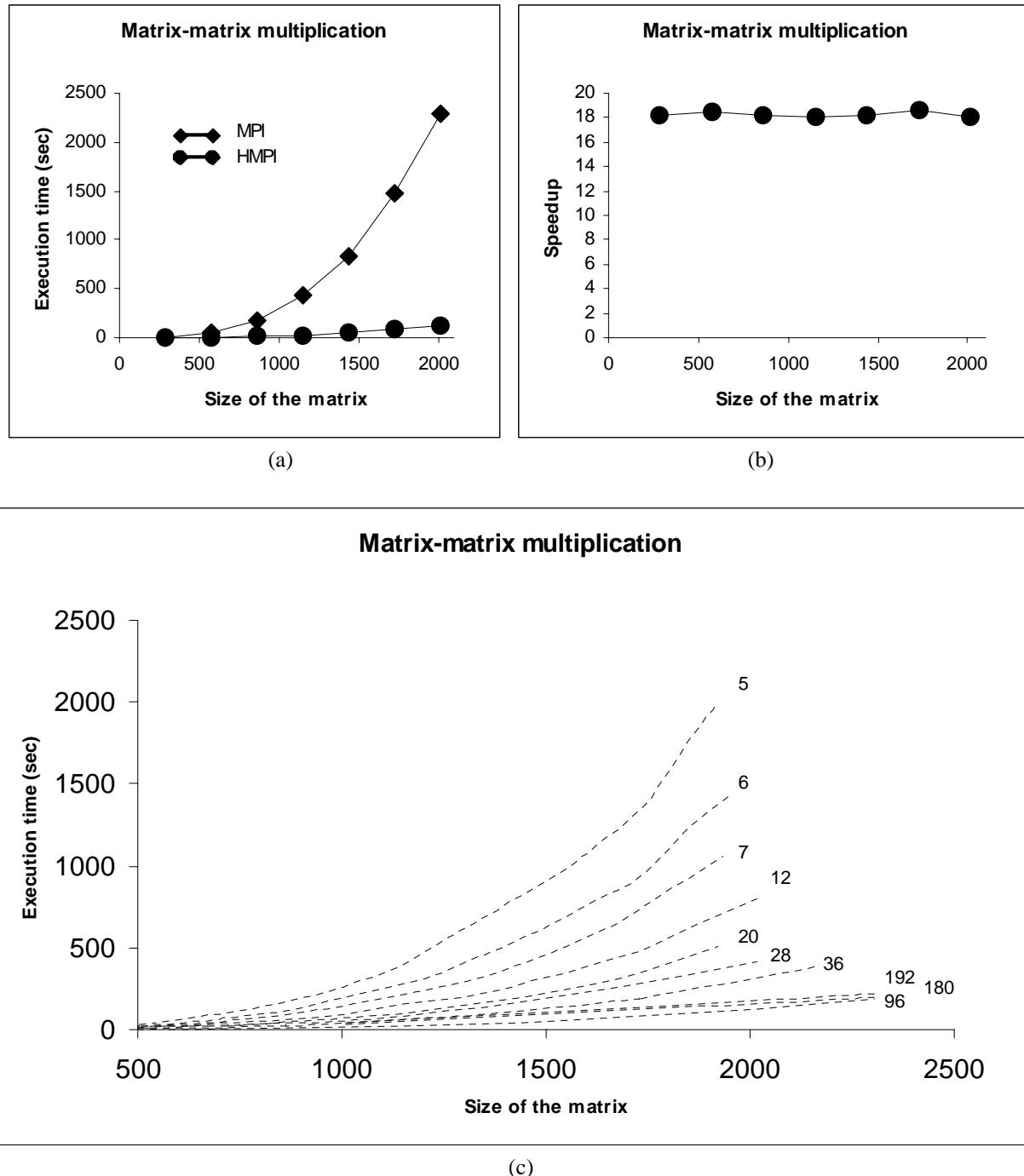

| 5.3                                                                                                                               | <i>Experiments with HMPI</i> .....                    | 343        |

| 5.3.1                                                                                                                             | <i>Building and Running an HMPI Application</i> ..... | 343        |

| 5.3.2                                                                                                                             | <i>Numerical Results</i> .....                        | 344        |

| 5.4                                                                                                                               | <i>Summary</i> .....                                  | 356        |

| <b>6</b>                                                                                                                          | <b>Conclusions</b> .....                              | <b>359</b> |

| 6.1                                                                                                                               | <i>Contributions</i> .....                            | 361        |

| <b>7</b>                                                                                                                          | <b>Future Work</b> .....                              | <b>367</b> |

| <b>List of References</b> .....                                                                                                   |                                                       | <b>380</b> |

| <b>Appendix A: Generated Code from Compiling Performance Model Definition of Parallel Simulation of Evolution of Bodies</b> ..... |                                                       | <b>396</b> |

| <b>Appendix B: HMPI Programmers' Reference and Installation Manual</b> .....                                                      |                                                       | <b>401</b> |

## Table of Figures

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

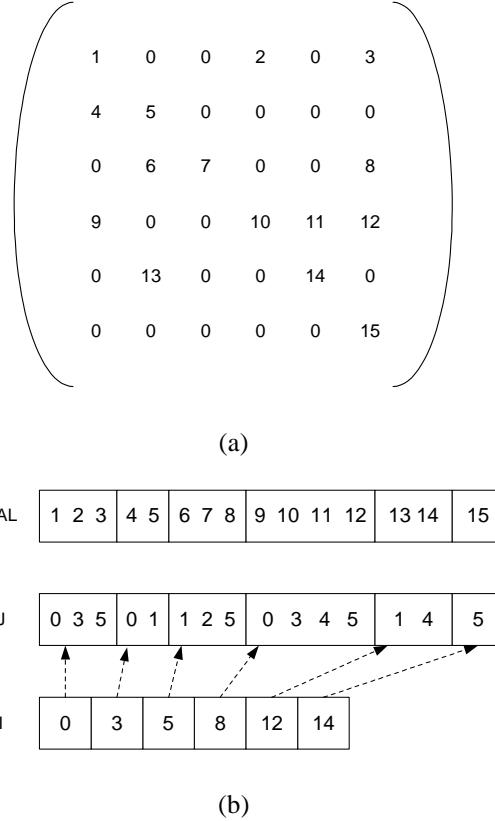

| 2.1 | A $6 \times 6$ sparse matrix and its representation in Compressed Storage Row (CSR) format.                                                                                                                                                                                                                                                                                                                                                                                                     | 24 |

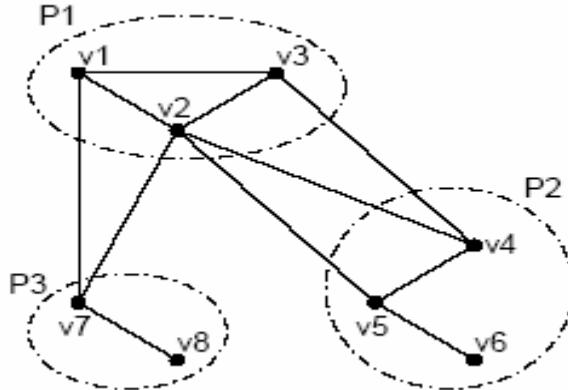

| 2.2 | Edge cuts versus communication volume.                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 26 |

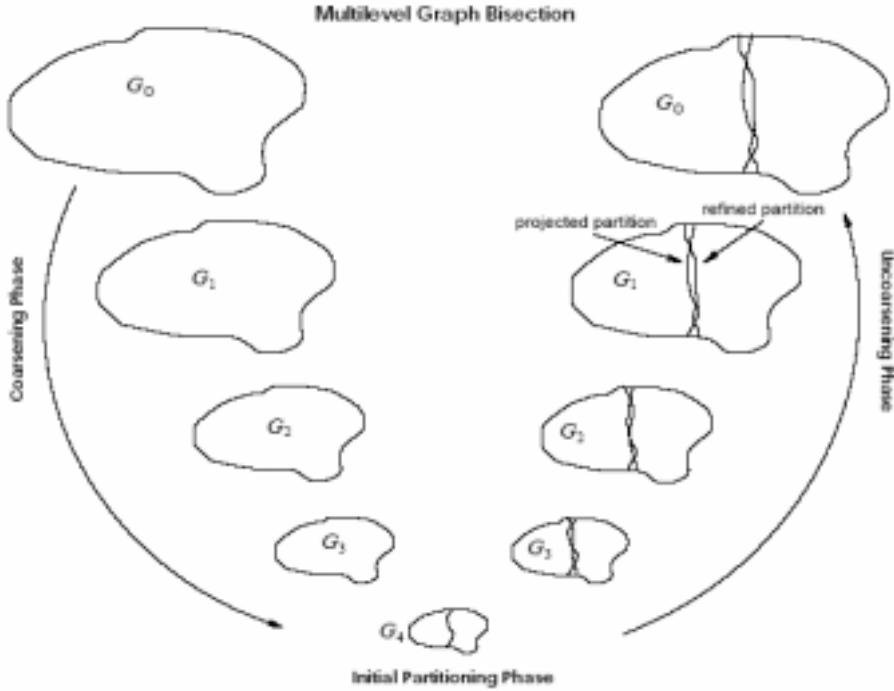

| 2.3 | The various phases of the multilevel graph bisection. During the coarsening phase, the size of the graph is successively decreased; during the initial partitioning phase, a bisection of the smaller graph is computed; and during the uncoarsening phase, the bisection is successively refined as it is projected to the larger graphs. During the uncoarsening phase the light lines indicate projected partitions, and dark lines indicate partitions that were produced after refinement. | 30 |

| 2.4 | A sample graph.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 32 |

| 2.5 | General procedure for a Genetic Algorithm, based on [SP94].                                                                                                                                                                                                                                                                                                                                                                                                                                     | 54 |

| 3.1 | The most relevant fragments of code of the ScaLAPACK program computing matrix-matrix multiplication using <b>PDGEMM</b> .                                                                                                                                                                                                                                                                                                                                                                       | 75 |

| 3.2 | The most relevant fragments of generated HMPI code computing matrix-matrix multiplication using <b>PDGEMM</b> on heterogeneous networks.                                                                                                                                                                                                                                                                                                                                                        | 76 |

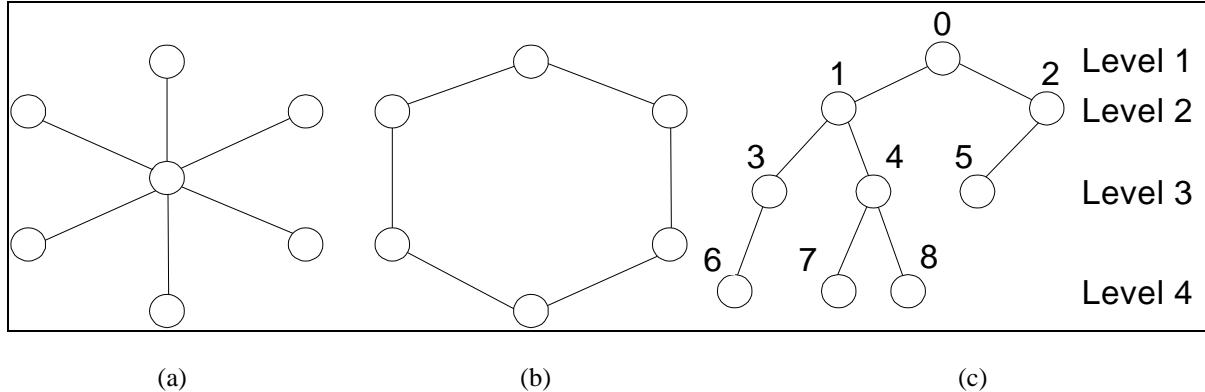

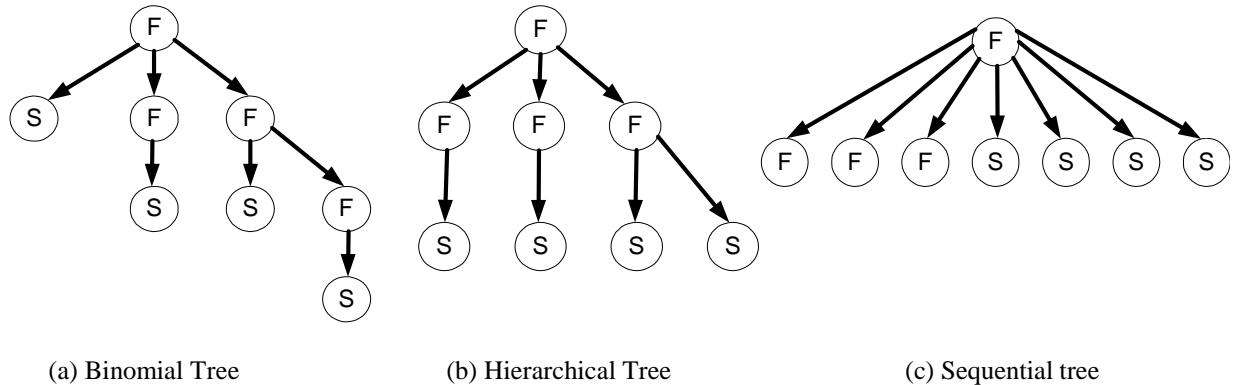

| 3.3 | The pattern of communication among the processors. (a) A star communication pattern, (b) A ring communication pattern, and (c) A tree communication pattern.                                                                                                                                                                                                                                                                                                                                    | 83 |

| 3.4 | A simple HMPI application that calls HMPI runtime initialization, group creation and HMPI runtime finalization.                                                                                                                                                                                                                                                                                                                                                                                 | 90 |

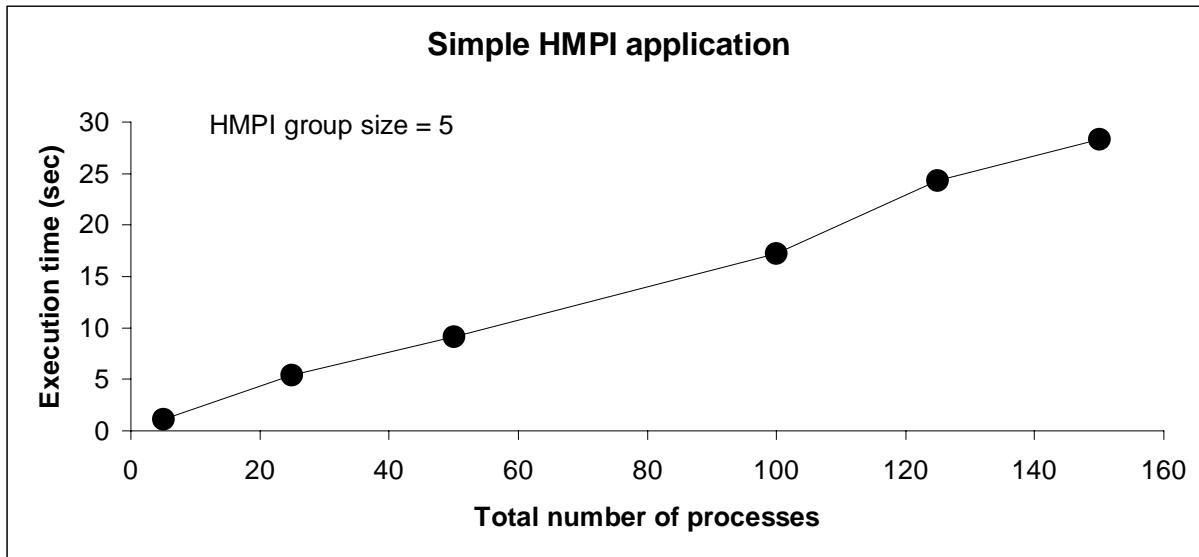

| 3.5 | Demonstration of the influence of the growth of the number of processes on the overhead associated with HMPI group creation and destruction. The execution times are for a simple HMPI application shown in Figure 3.4 run on the network shown in Table 3.1.                                                                                                                                                                                                                                   |    |

Only 5 processes are members of the HMPI group and are involved in the execution of the algorithm whereas the rest of the processes are idle and not involved in any computations. For the first point, a process is run on each computer of the network. For experimental point **i** ( $i > 1$ ),  $5 \times i$  processes are run on each computer of the network.

|                                                                                                                                                                                                                                                                                                |     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| .....                                                                                                                                                                                                                                                                                          | 91  |

| 3.6 A simple HMPI application that calls HMPI runtime initialization, group creation and HMPI runtime finalization (HMPI group consists of one process per processor). .....                                                                                                                   | 92  |

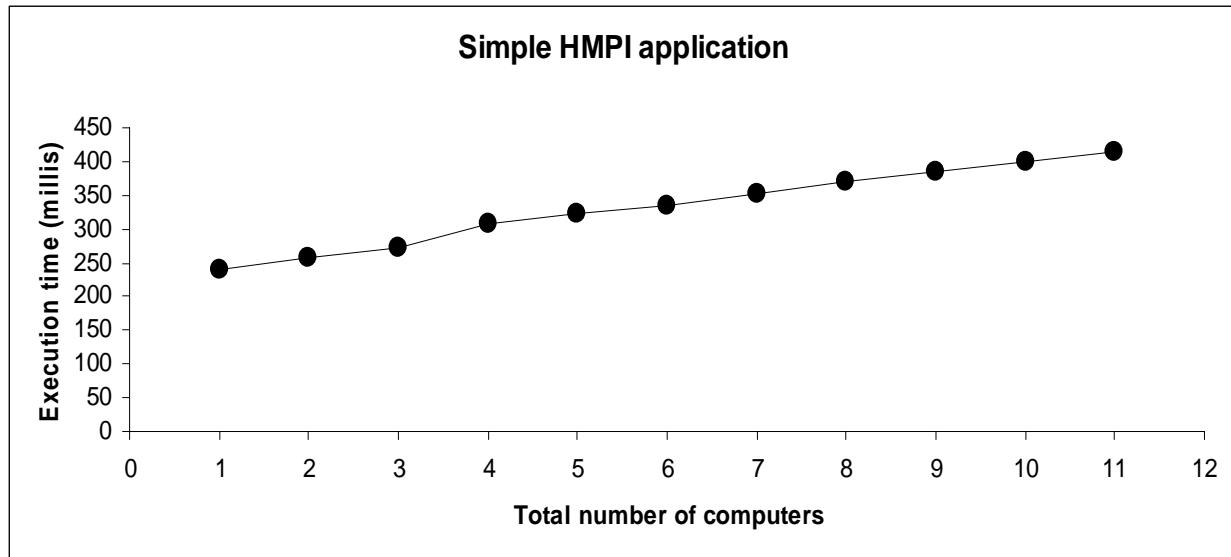

| 3.7 Demonstration of the influence of the growth of the number of computers on the overhead associated with HMPI group creation and destruction. The execution times are for a simple HMPI application shown in Figure 3.6 run on the network shown in Table 3.2. .....                        | 93  |

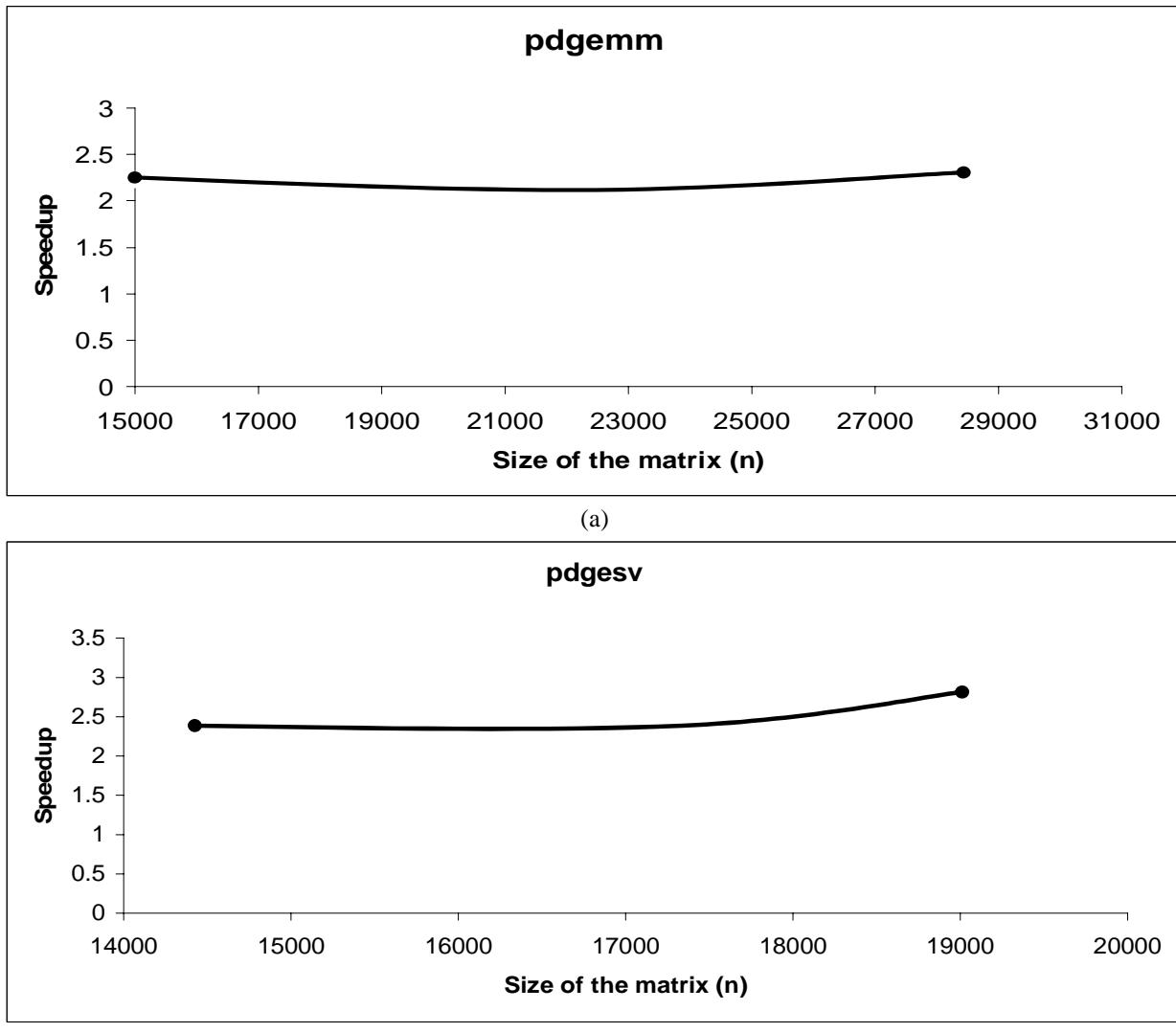

| 3.8 Results obtained using the network of heterogeneous computers shown in Table 3.3. (a) Comparison of speedups of matrix-matrix multiplication using the routine <b>pdgemm</b> . (b) Comparison of speedups of solving linear system of equations using the routine <b>pdgesv</b> .<br>..... | 96  |

| 3.9 Specification of the performance model of the parallel algorithm of the simulation of evolution of bodies in the HMPI's performance definition language. .....                                                                                                                             | 99  |

| 3.10 The most principal code of the HMPI program illustrating the creation of the optimal group of processes using the operation <b>HMPI_Group_create</b> . .....                                                                                                                              | 99  |

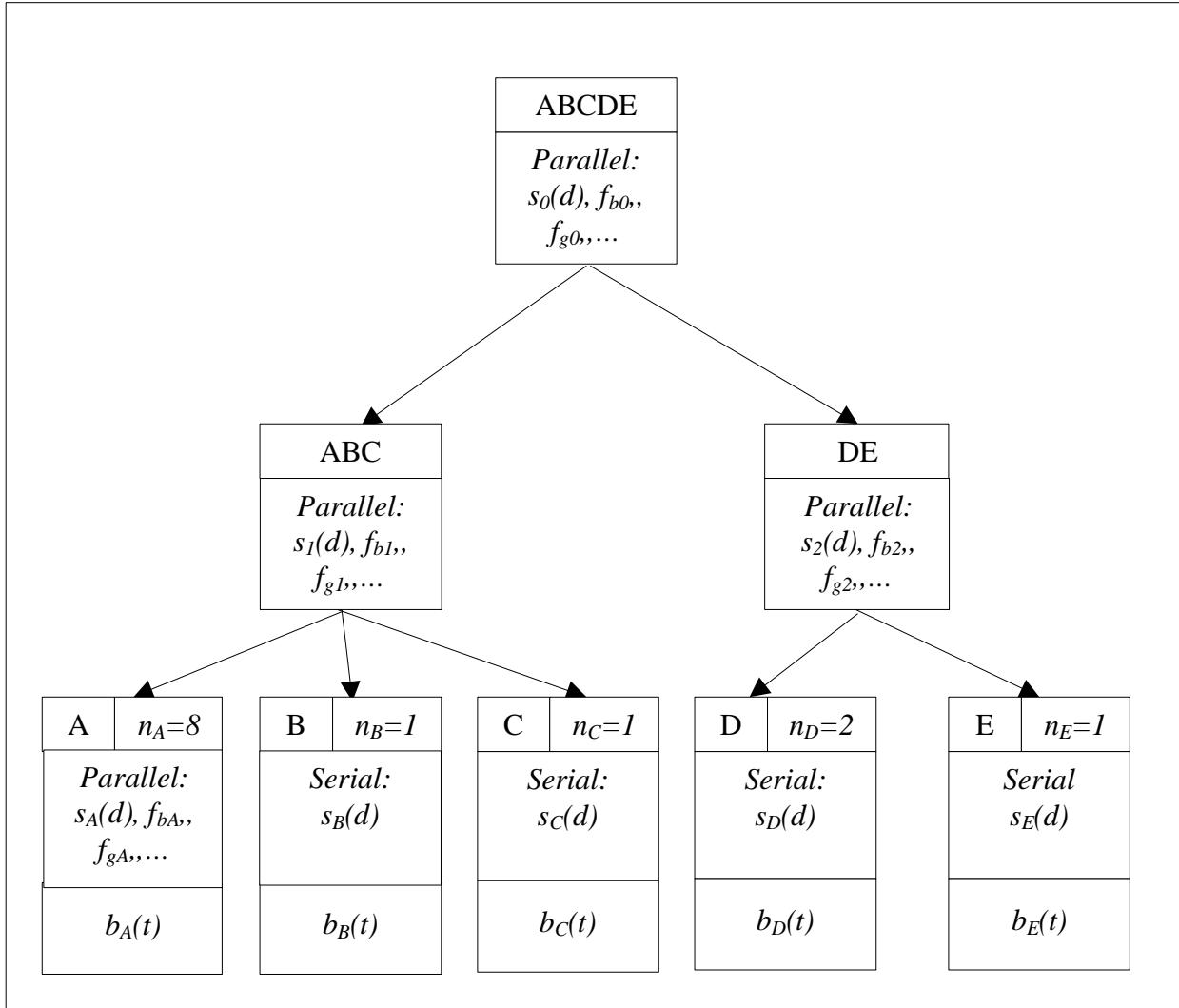

| 3.11 Hierarchical model of a heterogeneous network of five computers. .....                                                                                                                                                                                                                    | 106 |

| 3.12 An example illustrating the usage of the operation <b>HMPI_Recon</b> to write parallel programs sensitive to dynamic changing loads. .....                                                                                                                                                | 113 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

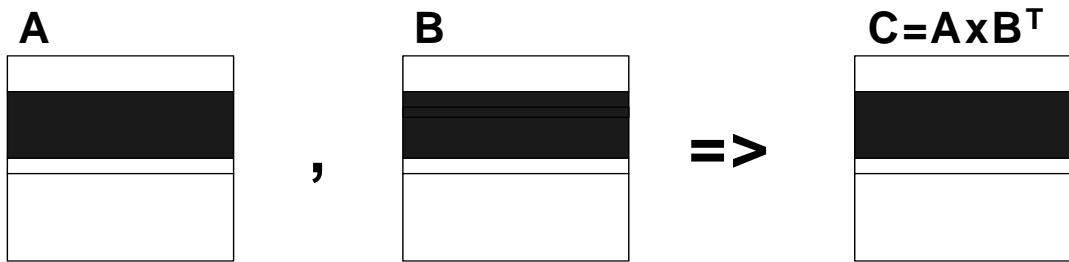

| 3.13 | Matrix operation $C = A \times B^T$ with matrices A, B, and C unevenly partitioned in one dimension. The slices mapped onto a single processor are shaded in black. ....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 132 |

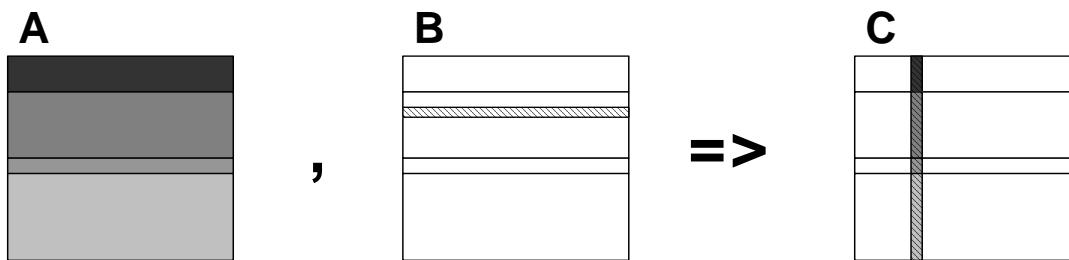

| 3.14 | One step of parallel multiplication of matrices A and B. The pivot row of matrix B (shown slashed) is first broadcast to all processors. Then each processor computes, in parallel with the others, its part of the corresponding column of the resulting matrix C. ....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 132 |

| 3.15 | Specification of the performance model of an algorithm of parallel matrix multiplication in the HMPI's performance definition language. ....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 134 |

| 3.16 | The most principal fragments of the usage of function <b>HMPI_Group_auto_create</b> for detection of the optimal subset of processors to execute the parallel matrix multiplication and creation of the corresponding optimal group of processes (one process per processor configuration is assumed). ....                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 135 |

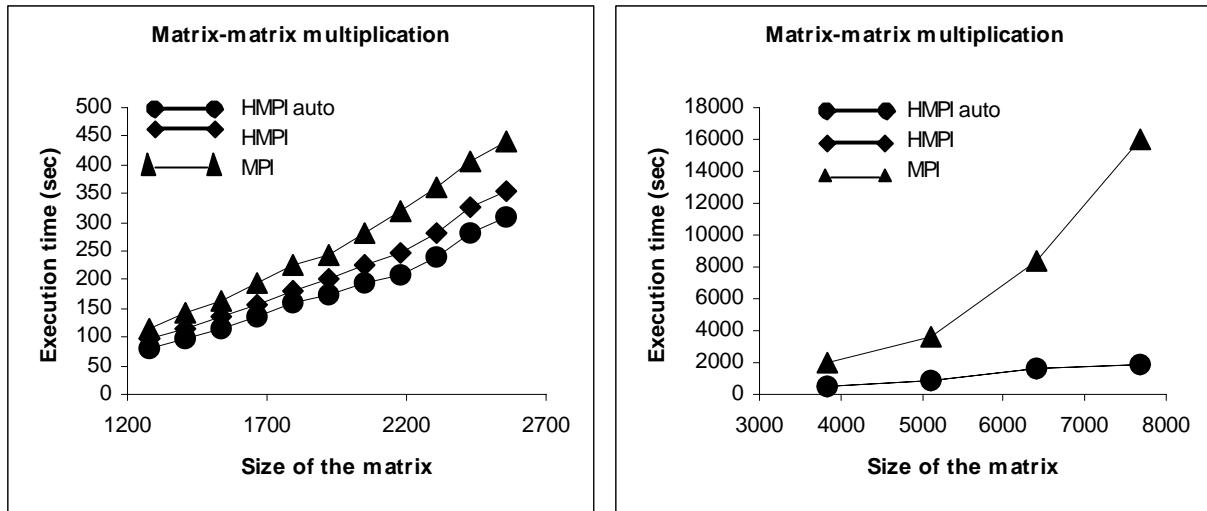

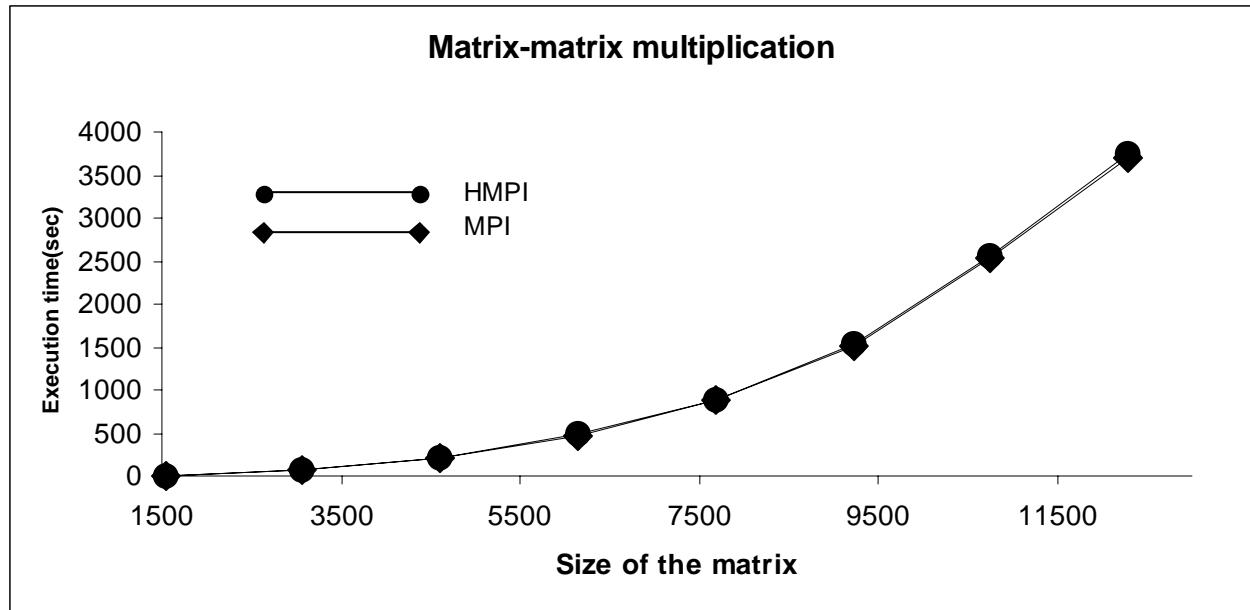

| 3.17 | Results obtained using the heterogeneous network of computers shown in Table 3.6. The results for ‘ <b>HMPI auto</b> ’ are for the HMPI application using the function <b>HMPI_Group_auto_create</b> . The results for ‘ <b>HMPI</b> ’ are for the HMPI application using the function <b>HMPI_Group_auto_create</b> and ‘ <b>MPI</b> ’ are for the MPI application using all the available 16 processes. (a) Comparison of execution times of Matrix-matrix multiplication using horizontal striped partitioning of matrices for the sizes of the matrix in the range 1000-3000. (b) Comparison of execution times of Matrix-matrix multiplication using horizontal striped partitioning of matrices for the sizes of the matrix in the range 3000-8000. .... | 139 |

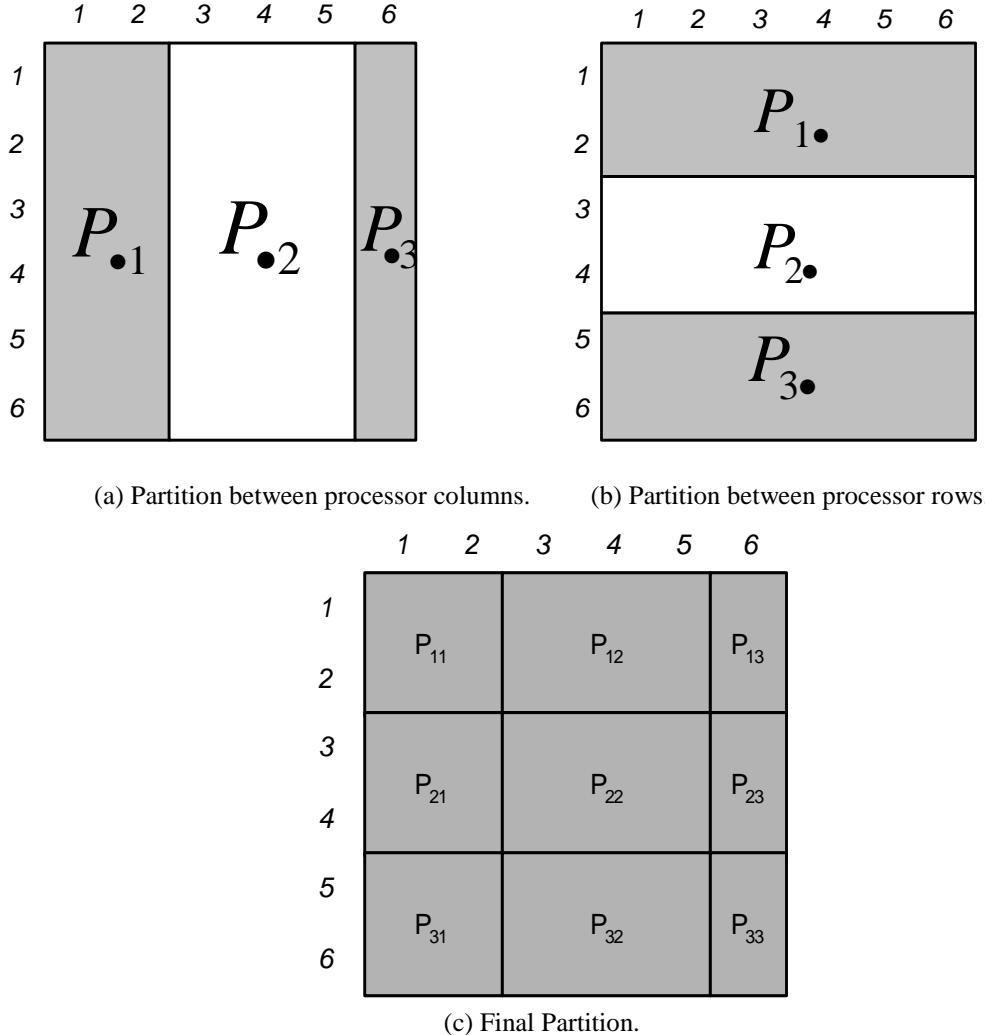

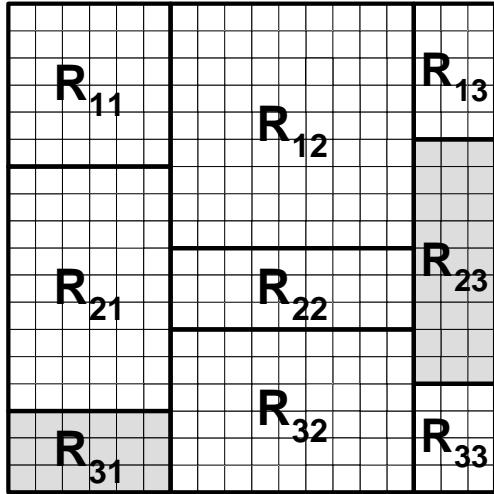

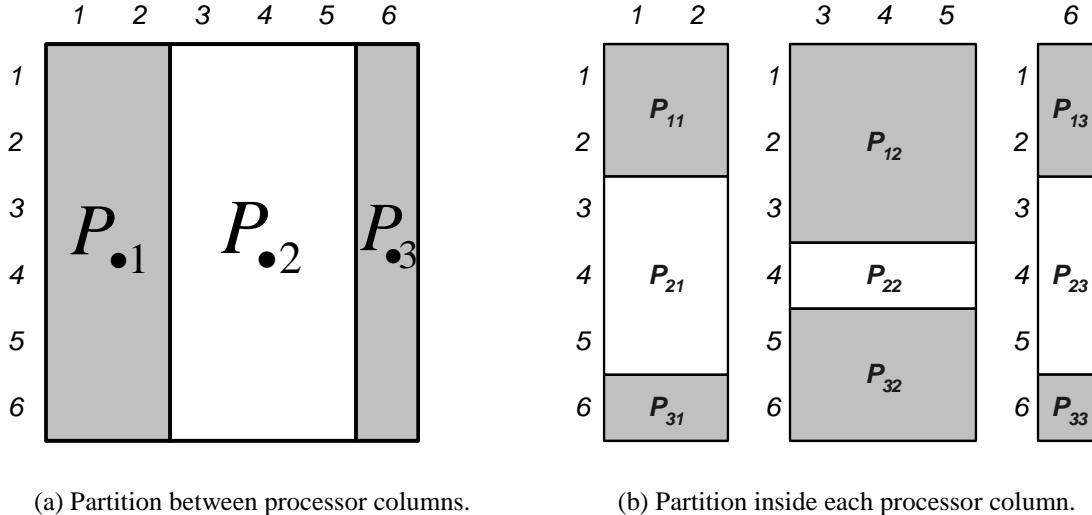

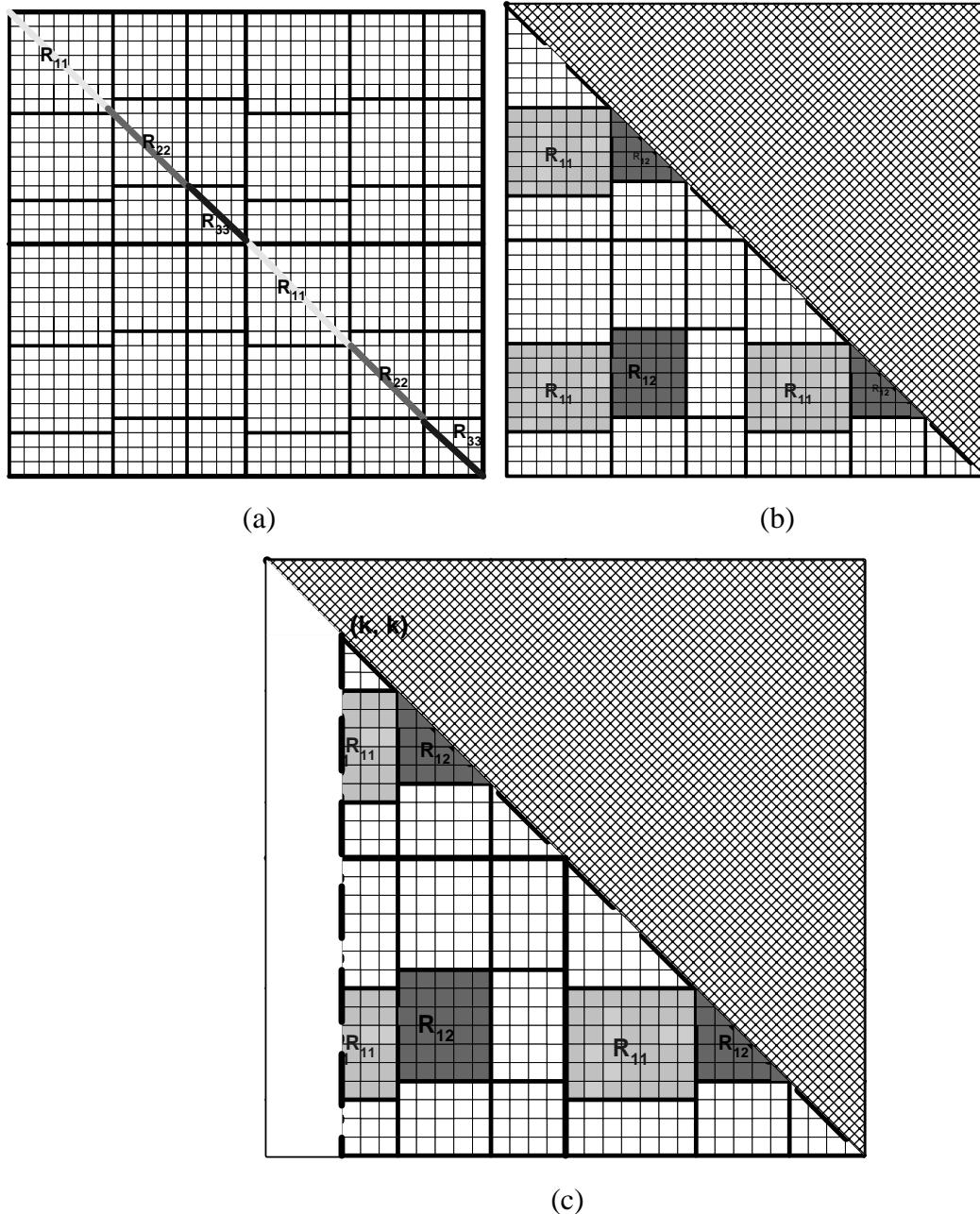

3.18 Example of two-step Cartesian distribution of a  $6 \times 6$  generalized block over a  $3 \times 3$  processor grid. The relative speed of processors is given by matrix

$$s = \begin{pmatrix} 0.11 & 0.17 & 0.05 \\ 0.17 & 0.09 & 0.08 \\ 0.05 & 0.25 & 0.03 \end{pmatrix}. \text{(a) At the first step, the } 6 \times 6 \text{ square is distributed in a one-dimensional block fashion over processors columns of the } 3 \times 3 \text{ processor grid in proportion } 0.33:0.51:0.16 \approx 2:3:1. \text{(b) At the second step, the } 6 \times 6 \text{ square is distributed in a one-dimensional block fashion over processors rows of the } 3 \times 3 \text{ processor grid in proportion } 0.33:0.34:0.33 \approx 2:2:2. \text{(c) Final partition. ....} 141$$

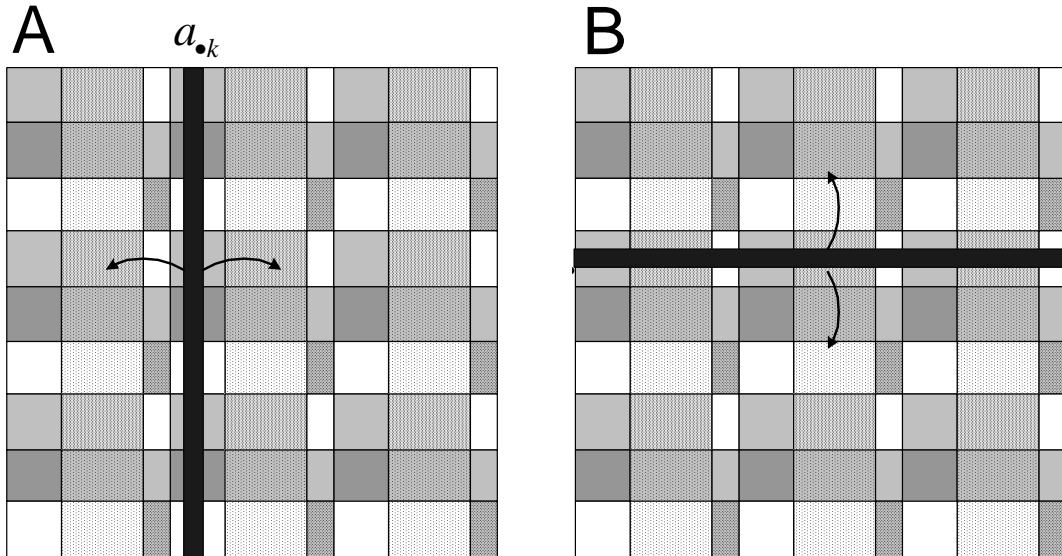

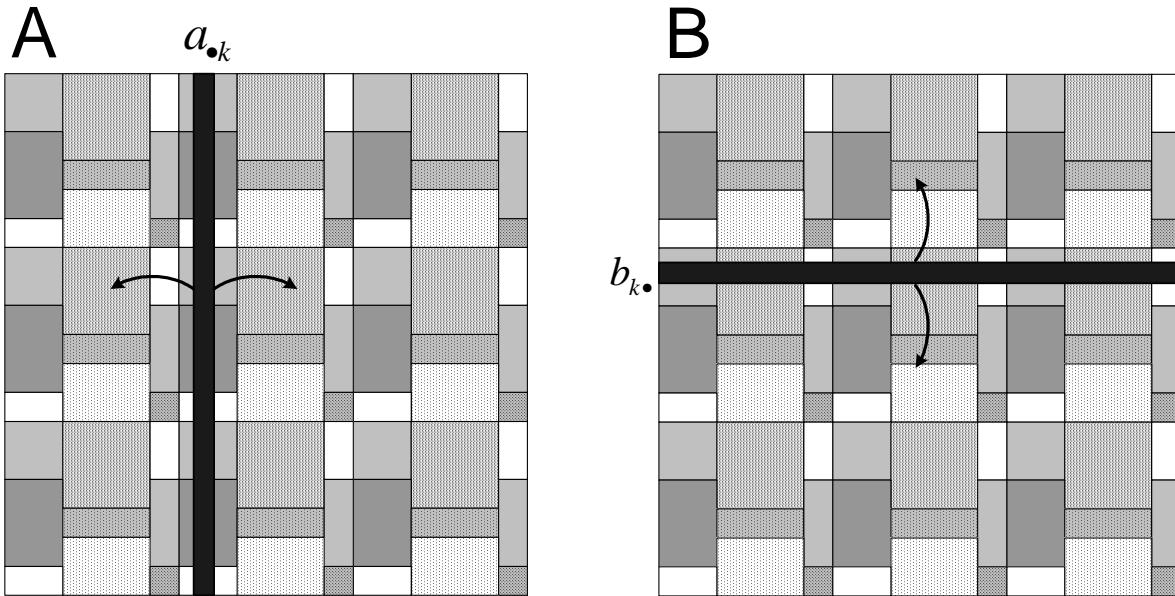

3.19 One step of the algorithm of parallel matrix-matrix multiplication based on heterogeneous two-dimensional block distribution of matrices A, B, and C. First, each  $r \times r$  block of the pivot column  $a_{\bullet k}$  of matrix A (shown shaded dark grey) is broadcast horizontally, and each  $r \times r$  block of the pivot row  $b_k$  of matrix B (shown shaded dark grey) is broadcast vertically. .... 143

3.20 Specification of the performance model of the algorithm of parallel matrix multiplication based on heterogeneous two-dimensional block-cyclic distribution of matrices in the HMPI's performance definition language. .... 144

3.21 The most principal fragments of the usage of function **HMPI\_Group\_auto\_create** for detection of the optimal processor grid arrangement to execute the parallel matrix multiplication implementing the algorithm of parallel matrix multiplication based on heterogeneous two-dimensional block-cyclic distribution of matrices and creation of the corresponding optimal group of processes (one process per processor configuration is assumed). .... 150

|      |                                                                                                                                                                                                                                                                                                                                                                 |     |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

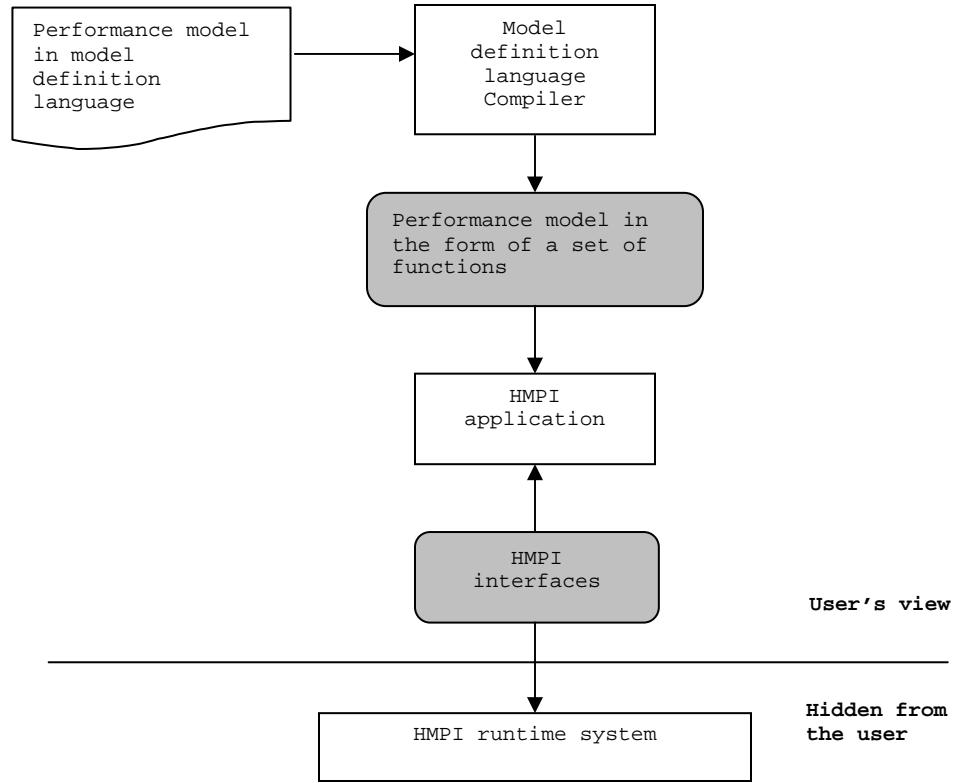

| 3.22 | Development process of an HMPI application. To build HMPI applications, an application programmer describes a performance model using the model definition language, compiles the performance model description into a set of functions, writes the application using the HMPI interfaces to create groups of processes to execute the parallel algorithm. .... | 158 |

| 3.23 | The most relevant fragments of code of the MPI program implementing the parallel matrix-matrix multiplication algorithm shown in Figures 3.11 and 3.12. ....                                                                                                                                                                                                    | 159 |

| 3.24 | The most relevant fragments of code of the HMPI program implementing the parallel matrix-matrix multiplication algorithm shown in Figures 3.11 and 3.12. ....                                                                                                                                                                                                   | 161 |

| 3.25 | HMPI program illustrating the coordinated arrival of processes at the epilogues of the waiting points. ....                                                                                                                                                                                                                                                     | 175 |

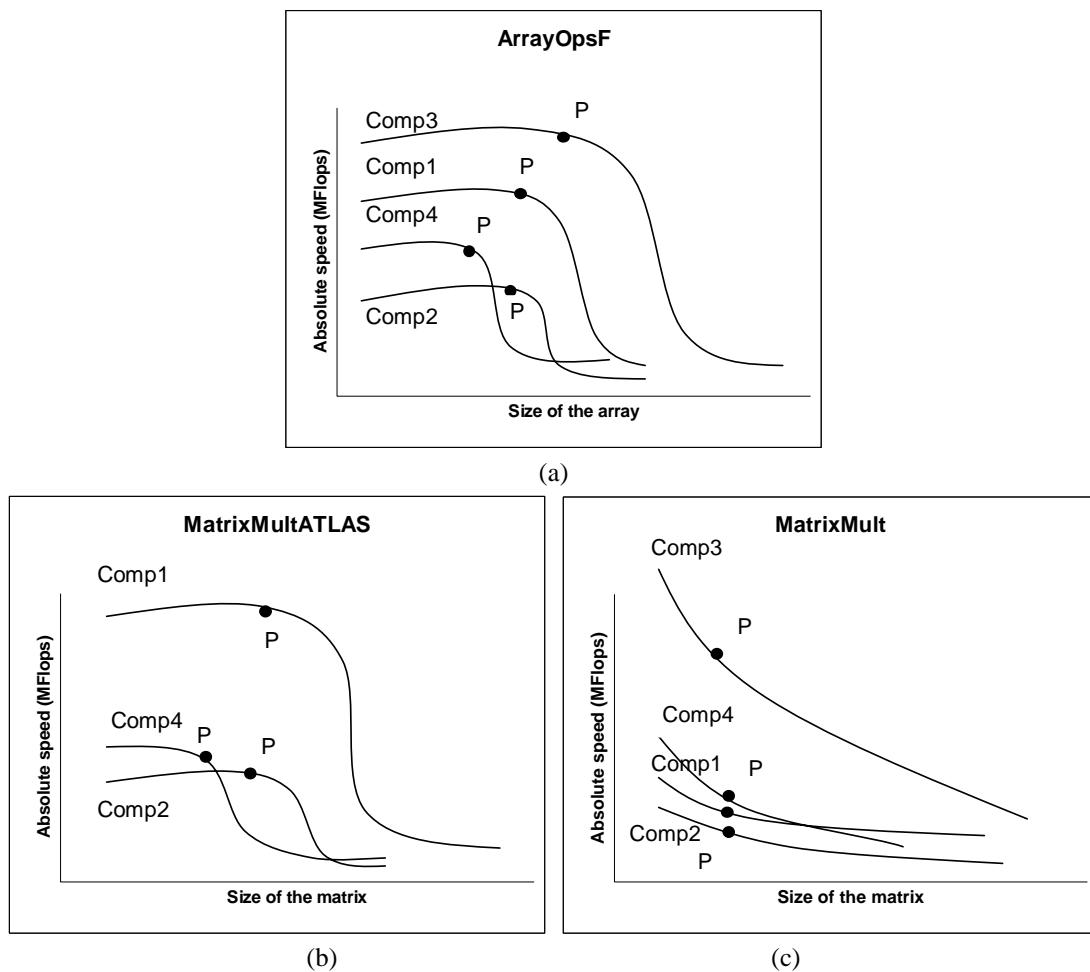

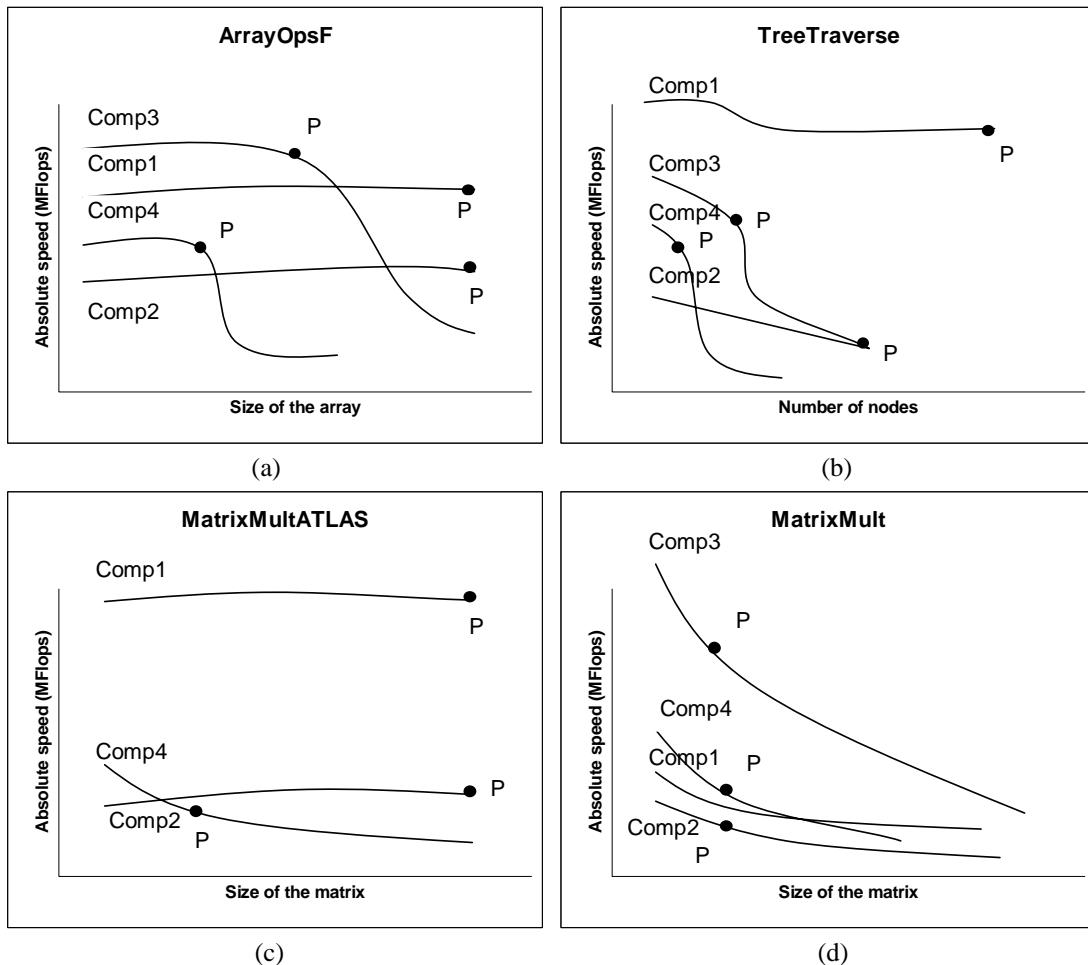

| 4.1  | The effect of caching and paging in reducing the execution speed of each of the four applications run on network of heterogeneous computers shown in Table 4.1. (a) ArrayOpsF, (b) MatrixMultATLAS, and (c) MatrixMult. P is the point where paging starts occurring. ....                                                                                      | 186 |

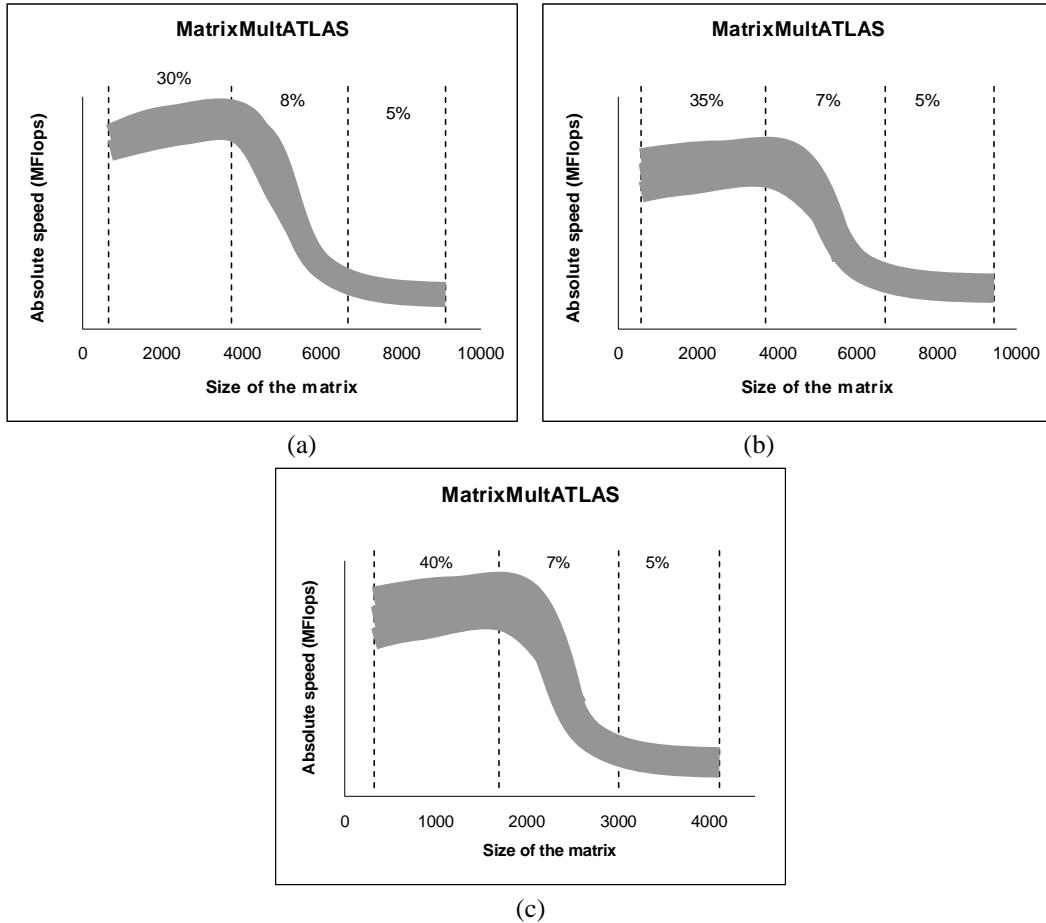

| 4.2  | Effect of workload fluctuations on the execution of application MatrixMultATLAS on computers shown in Table 4.1. The width of the performance bands is given in percentage of the maximum speed of execution of the application. (a) Performance band for Comp1, (b) Performance band for Comp2, and (c) Performance band for Comp4. ....                       | 188 |

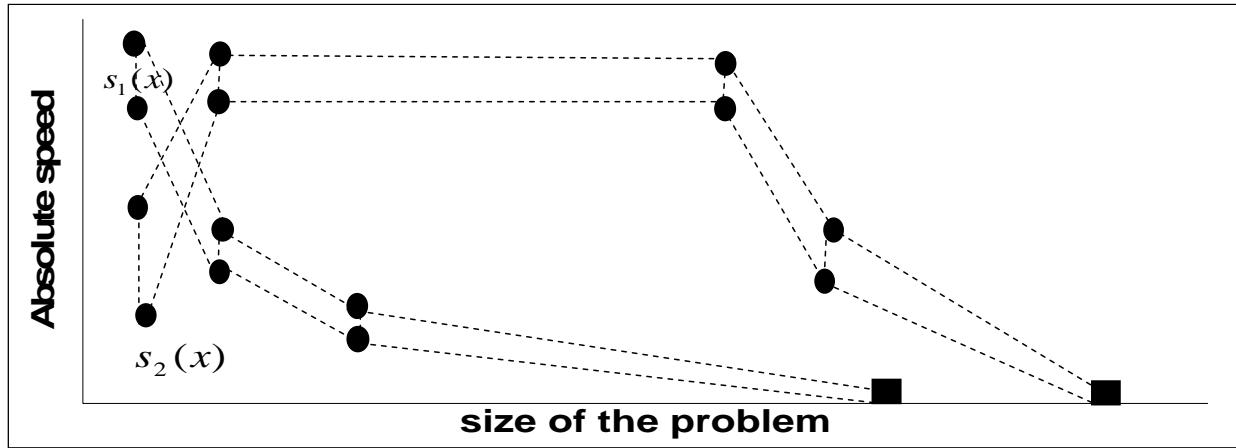

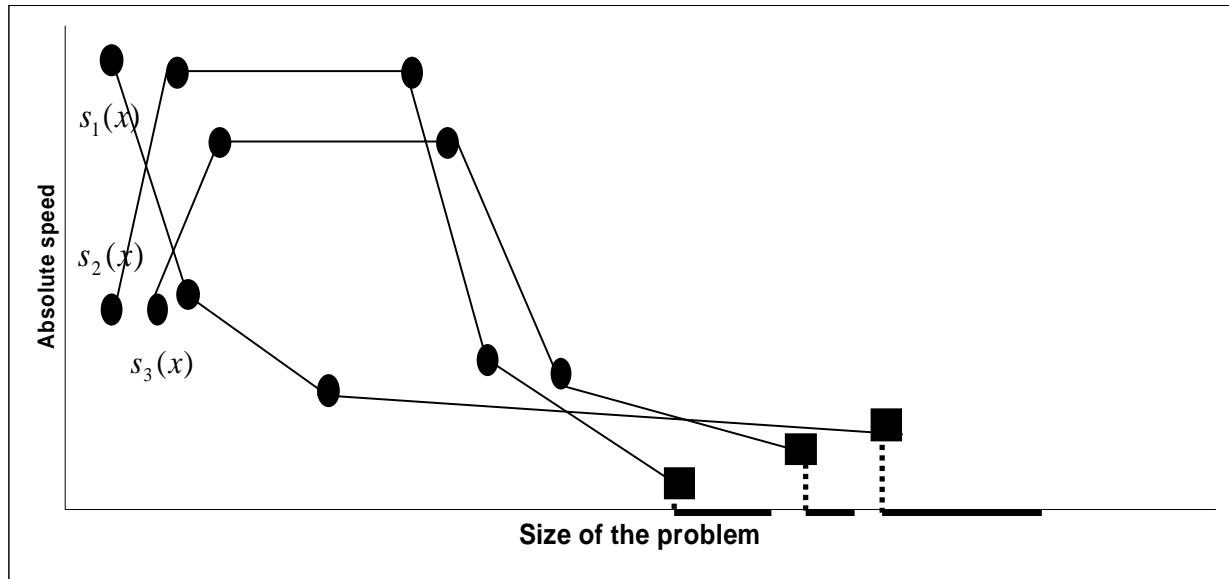

| 4.3  | Using piecewise linear approximation to build speed bands for 2 processors. The circular points are experimentally obtained whereas the square points are calculated using heuristics. The speed band for processor $s_1(x)$ is built from 3 experimentally obtained                                                                                            |     |

|                                                                                                                                                                                                                                                                                                                                                                                                               |     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| points (application run on this processor uses memory hierarchy inefficiently) whereas the speed band $s_2(x)$ (application run on this processor uses memory hierarchy efficiently) is built from 4 experimentally obtained points. ....                                                                                                                                                                     | 192 |

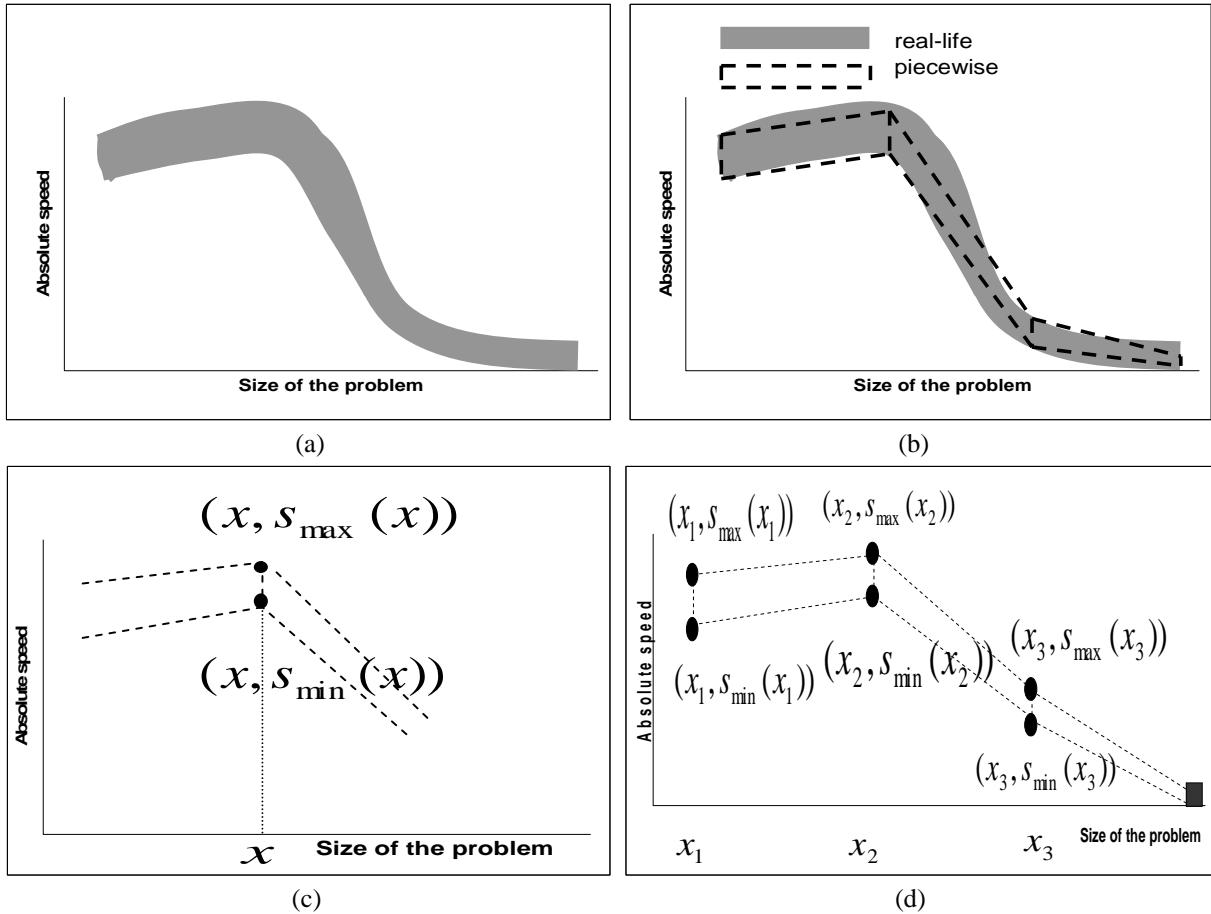

| 4.4 (a) Real-life speed band of a processor, (b) Real-life speed band of a processor and a piecewise linear function approximation of a processor, (c) The speeds $s_{\max}(x)$ and $s_{\min}(x)$ representing a cut of the real band used to build the piecewise linear approximation, and (d) Piecewise linear approximation built by connecting the cuts. ....                                             | 193 |

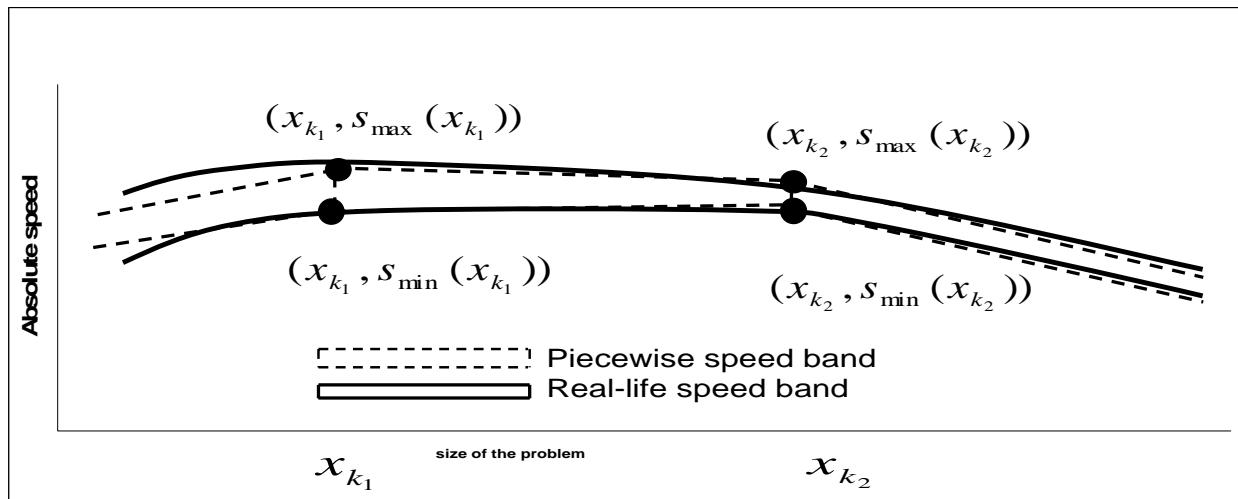

| 4.5 The non-empty intersectional area of piecewise linear function approximation with the real-life speed band is a simply connected surface. ....                                                                                                                                                                                                                                                            | 195 |

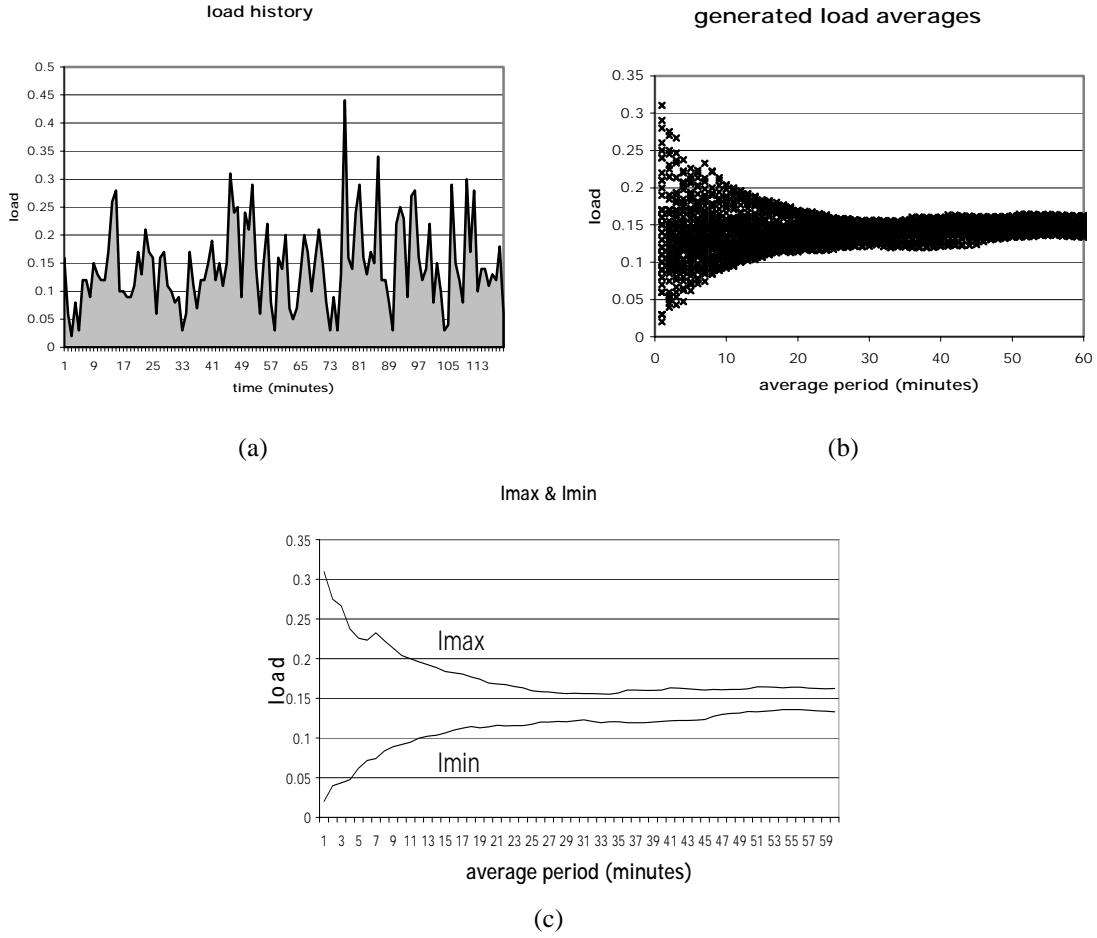

| 4.6 (a) $l_{\max}(t)$ and $l_{\min}(t)$ are generated from the load history. (b) A plot of points in matrix A. (c) $l_{\max}(t)$ and $l_{\min}(t)$ , the maximum and minimum loads calculated from the matrix of load averages A. ....                                                                                                                                                                        | 197 |

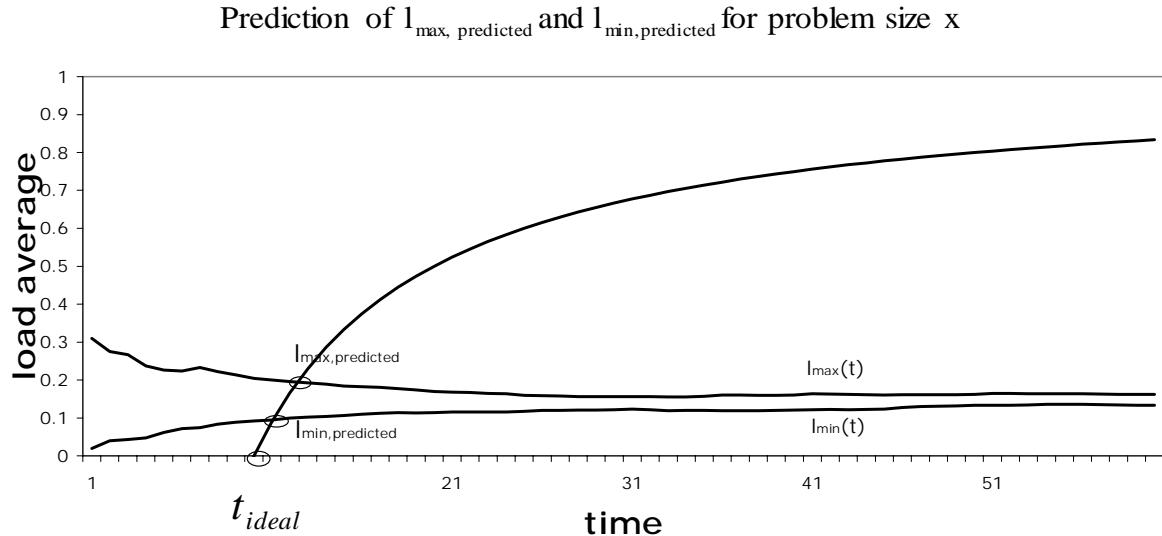

| 4.7 Intersection of load and running time functions (Formula 3). ....                                                                                                                                                                                                                                                                                                                                         | 200 |

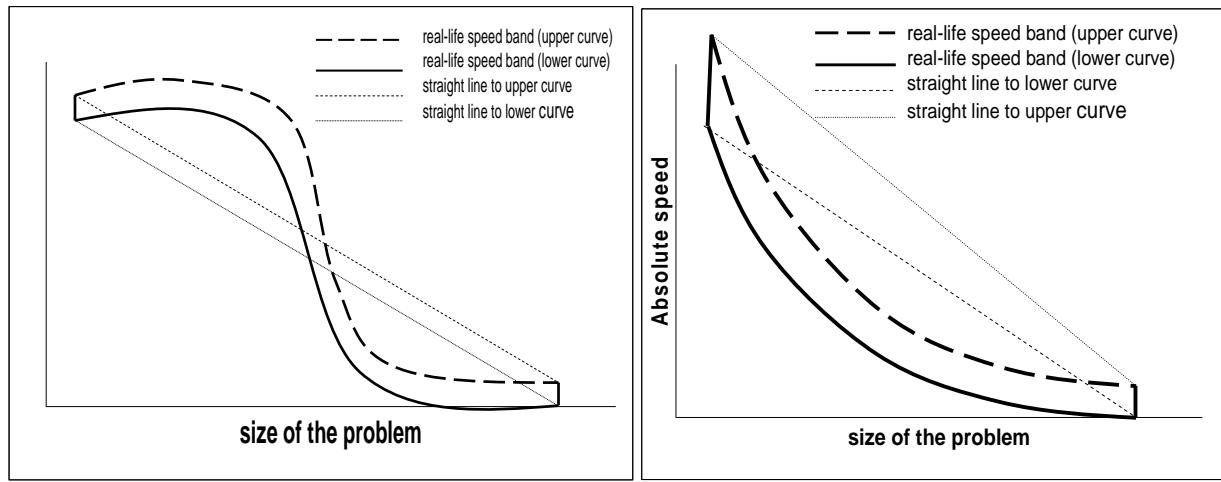

| 4.8 Permissible shapes of the graphs representing the real-life speed bands of two processors. ....                                                                                                                                                                                                                                                                                                           | 201 |

| 4.9 (a) Shape of real-life speed function of processor for applications that use memory hierarchy efficiently, (b) Shape of real-life speed function of processor for applications that use memory hierarchy inefficiently. ....                                                                                                                                                                              | 201 |

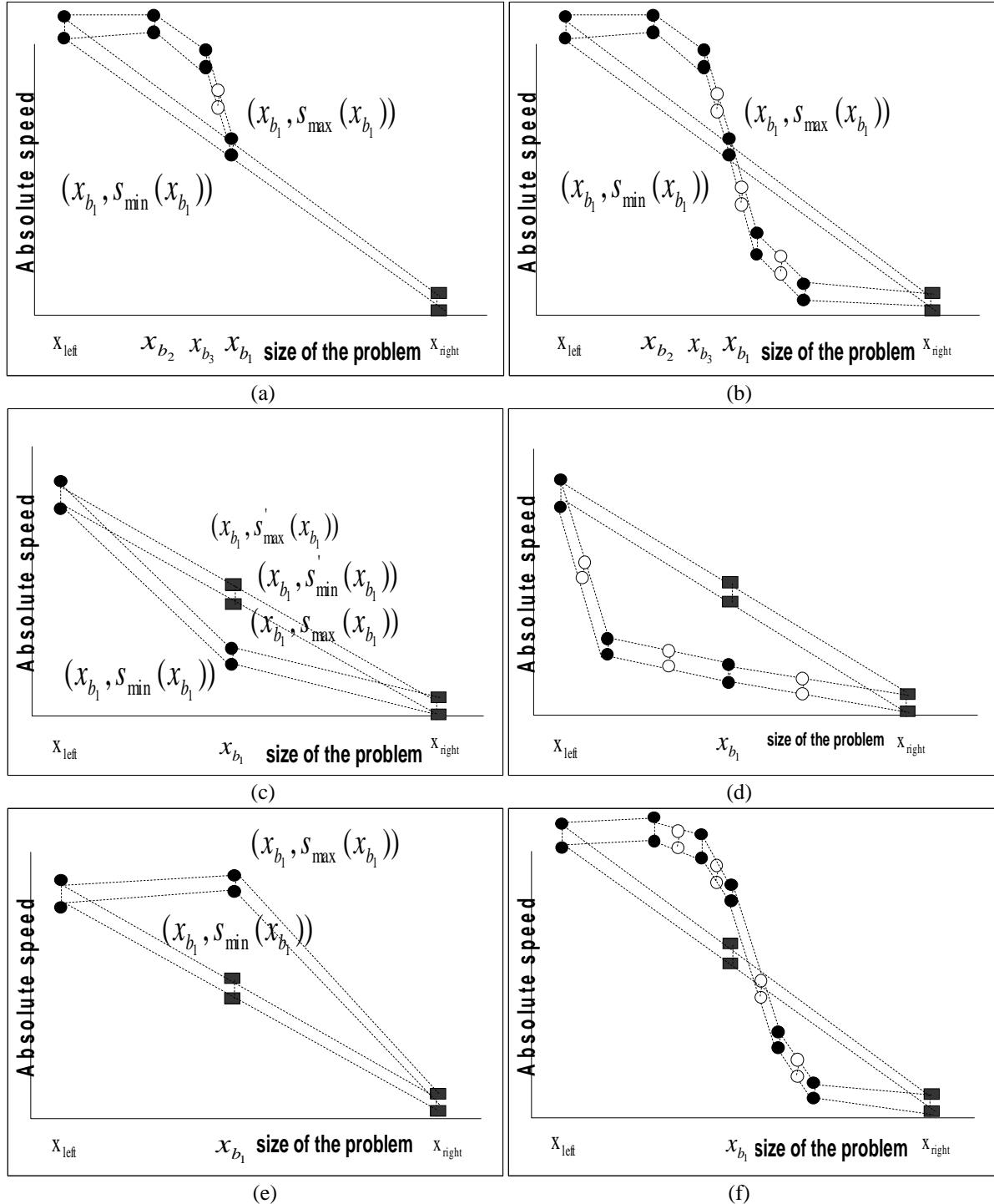

| 4.10 (a) to (f) Illustration of the procedure to obtain the piecewise linear function approximation of the speed band for a processor. Circular points are experimentally obtained points. Square points are points of intersection that are calculated but not experimentally obtained. White circular points are experimentally obtained and that fall in the current approximation of the speed band. .... | 203 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.11 | (a) to (f) Illustration of the procedure to obtain the piecewise linear function approximation of the speed band for a processor. Circular points are experimentally obtained points. Square points are points of intersection that are calculated but not experimentally obtained. White circular points are experimentally obtained and that fall in the current approximation of the speed band. ....                                                                                                                                                                    | 207 |

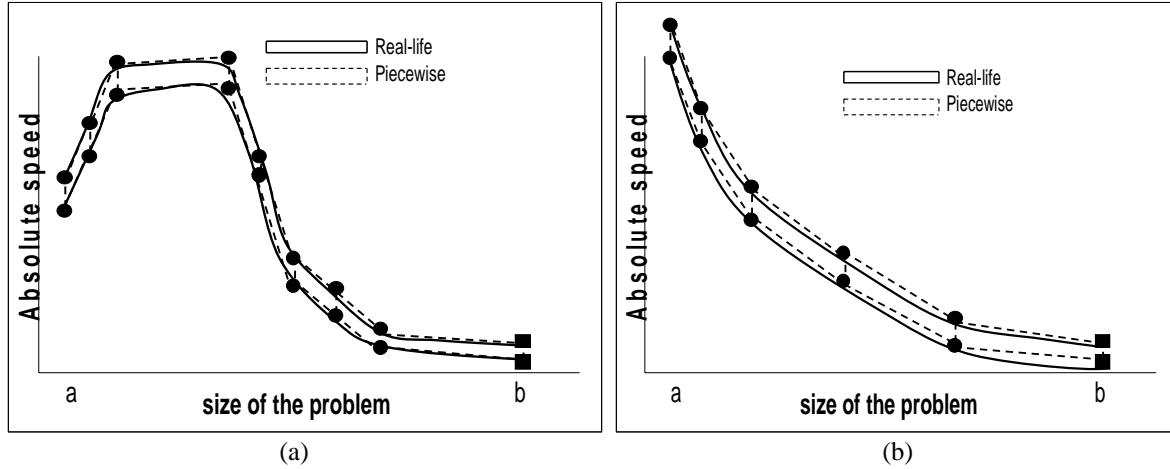

| 4.12 | (a) The final piecewise linear function approximation of the speed band of a processor for an application that utilizes memory hierarchy efficiently. (b) The final piecewise linear function approximation of the speed band of a processor for an application that utilizes memory hierarchy inefficiently. ....                                                                                                                                                                                                                                                          | 209 |

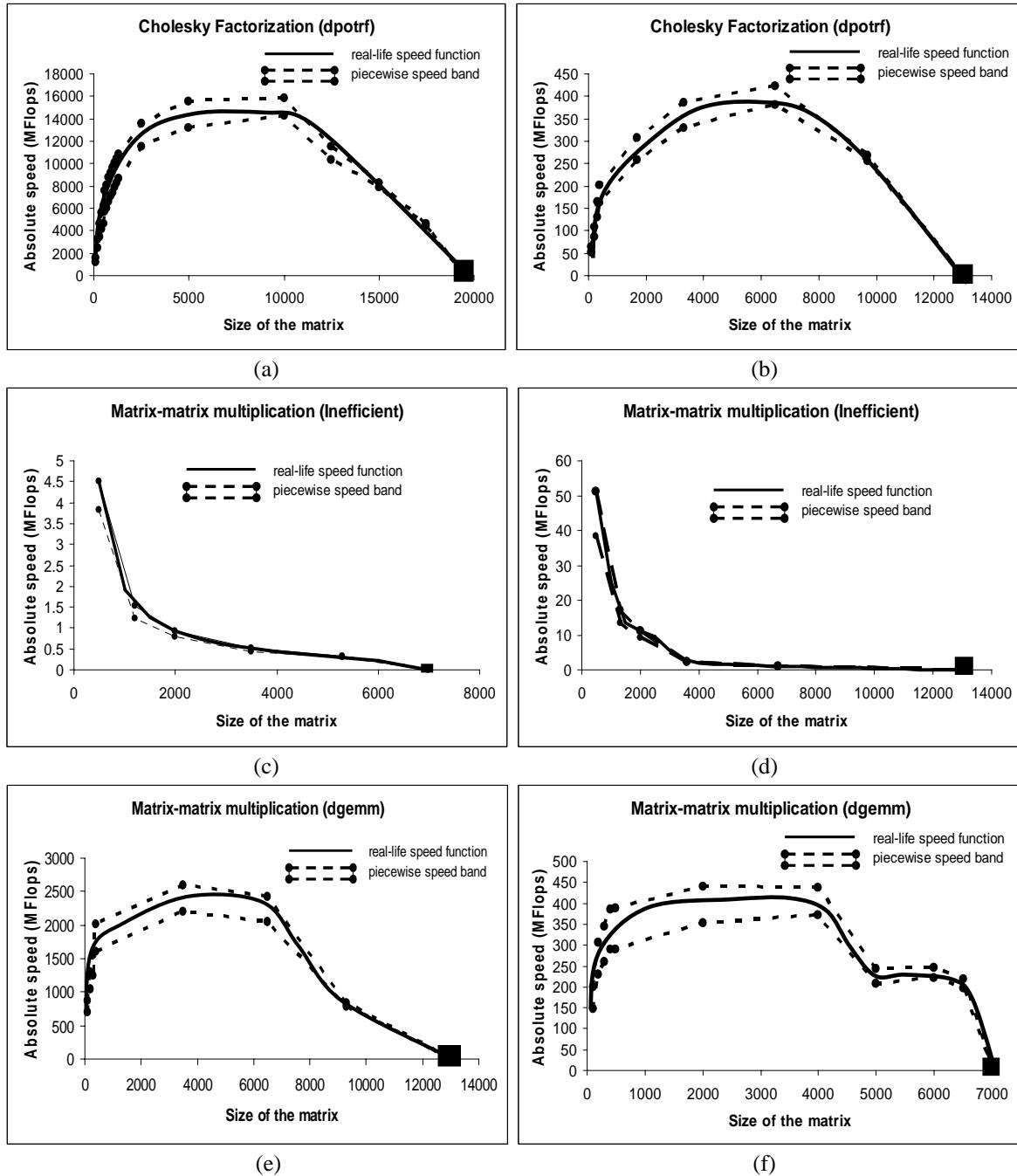

| 4.13 | Piecewise linear approximation of the speed band against the real-life speed function. Circular points are experimentally obtained points. Square points are calculated but not experimentally obtained. (a) Cholesky Factorization using ATLAS on X1. (b) Cholesky Factorization using ATLAS on X2. (c) Matrix-matrix multiplication using memory hierarchy inefficiently on X1. (d) Matrix-matrix multiplication using memory hierarchy inefficiently on X2. (e) Matrix-matrix multiplication using ATLAS on X1. (f) Matrix-matrix multiplication using ATLAS on X2. .... | 211 |

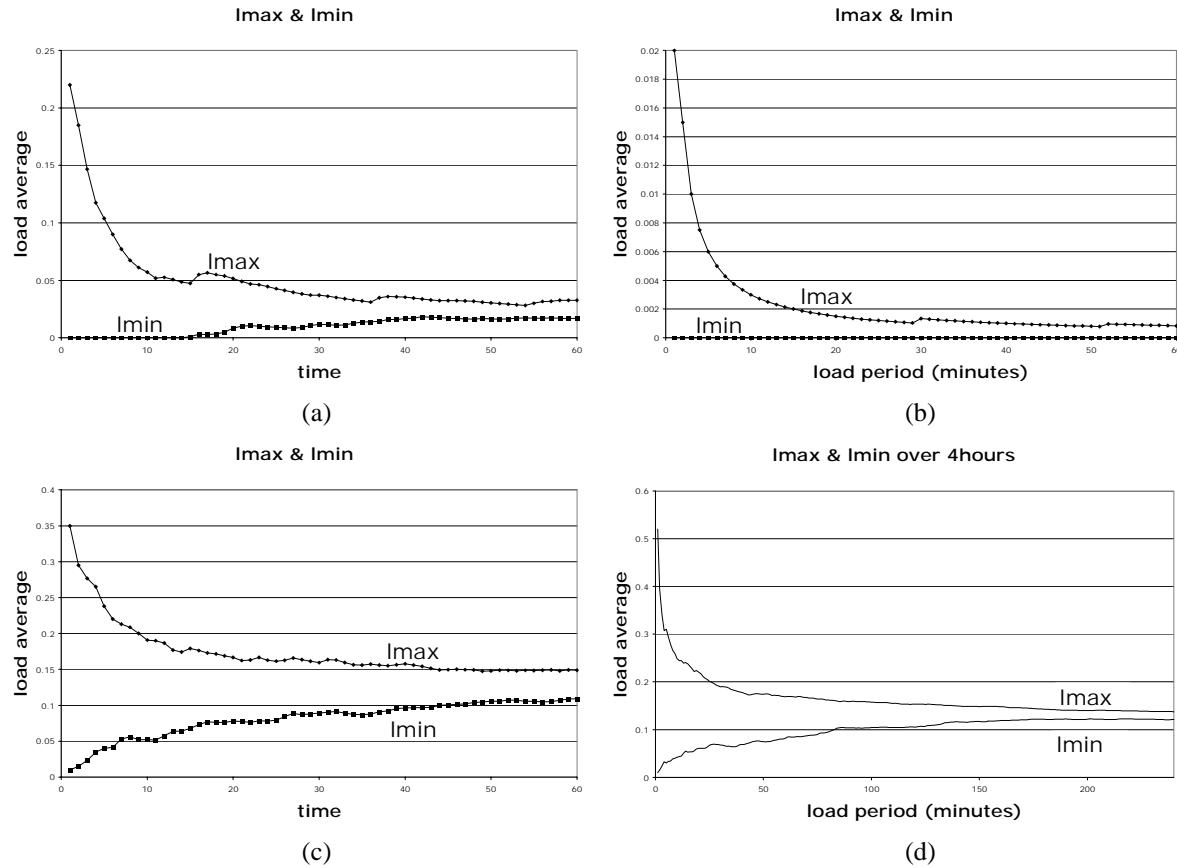

| 4.14 | (a) Load functions for X1. (b) Load functions for X2. (c) Load functions for a departmental server running loads at all times. (d) Load functions generated with average periods beyond one hour. ....                                                                                                                                                                                                                                                                                                                                                                      | 213 |

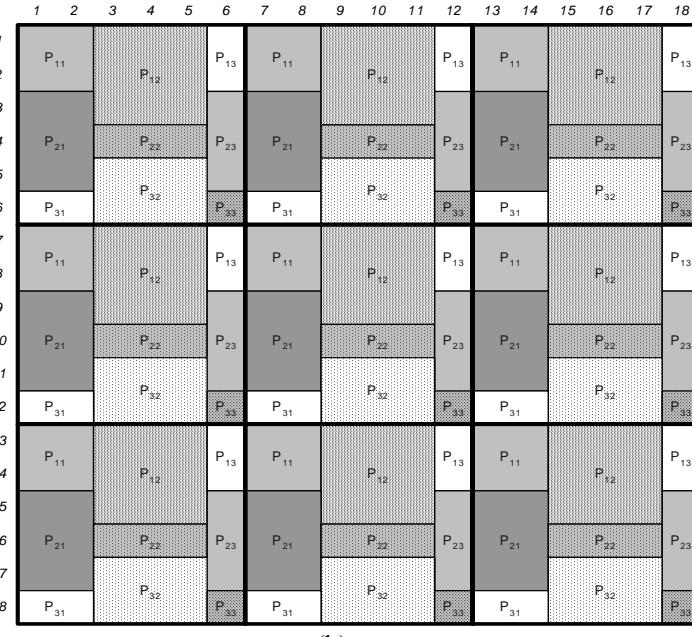

| 4.15 | (a) Homogeneous two-dimensional block-cyclic distribution of a matrix with $18 \times 18$ elements over a $3 \times 3$ processor grid; (b) Heterogeneous two-dimensional block-cyclic distribution of a matrix of size $18 \times 18$ elements with $6 \times 6$ generalized blocks distributed over a $3 \times 3$ processor grid. Each labeled (shaded and unshaded) area represents different                                                                                                                                                                            |     |

rectangles of blocks, and the label indicates at which location in the processor grid the rectangle is stored – all rectangles labeled with the same name are stored in the same processor. Each square in a bold frame represents different generalized blocks. ..... 224

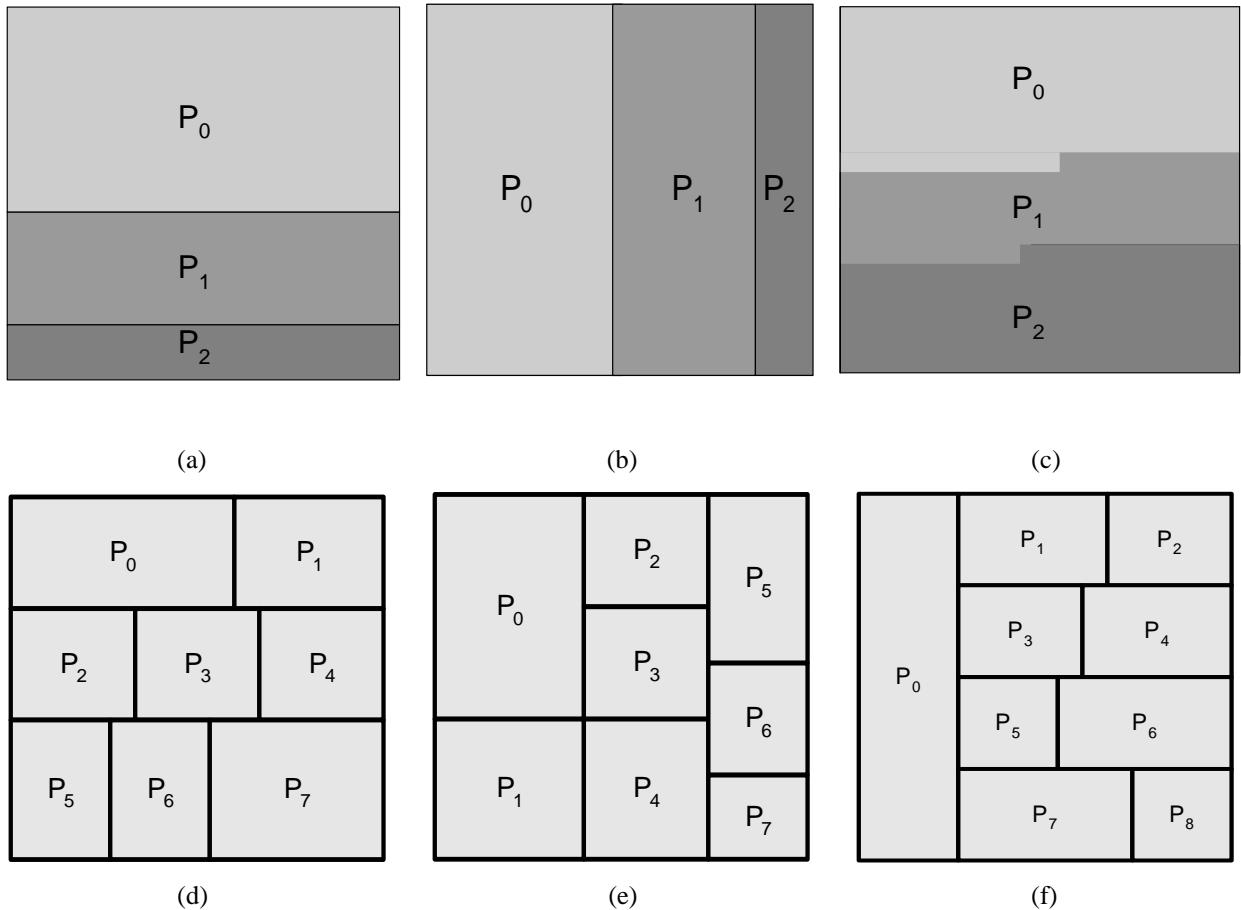

4.16 Types of distribution of a matrix over a linear processor array. (a) Horizontal sliced distribution of a generalized block over a linear array of 3 processors, (b) Vertical sliced distribution of a generalized block over a linear array of 3 processors, (c) Row-contiguous distribution of the elements of a generalized block over a linear array of 3 processors, (d) Generalized row-based distribution of a generalized block over a linear array of 8 processors, (e) Generalized column-based distribution of a generalized block over a linear array of 8 processors, and (f) General rectangular distribution of a generalized block over 9 processors. ..... 227

4.17 Types of distribution of a matrix over a two-dimensional grid of processors. (a) Two-dimensional Cartesian distribution of a generalized block over a  $3 \times 3$  processor grid, (b) Two-dimensional row-based distribution of a generalized block over a  $3 \times 3$  processor grid, and (c) Two-dimensional column-based distribution of a generalized block over a  $3 \times 3$  processor grid. ..... 228

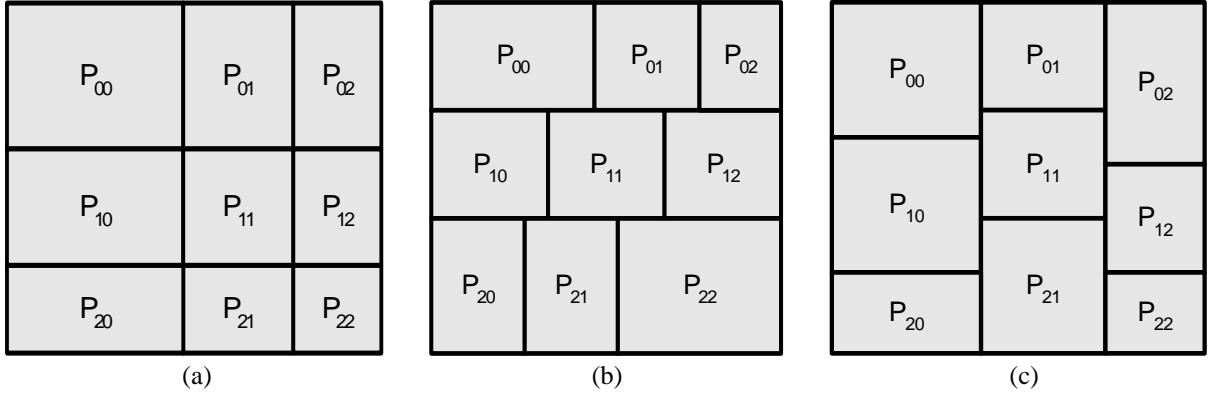

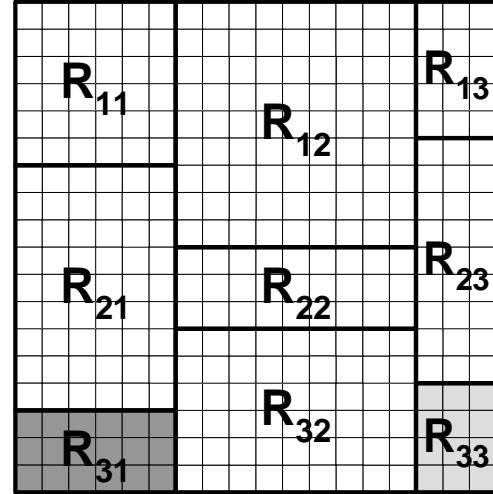

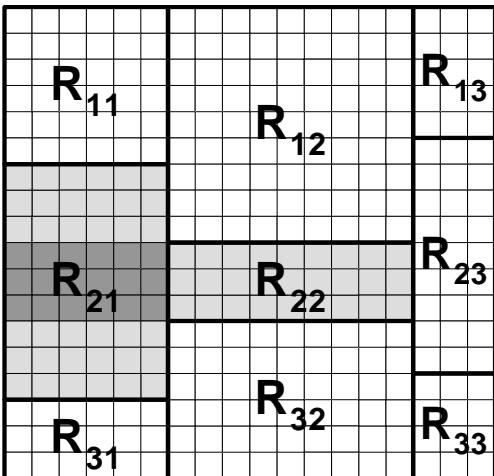

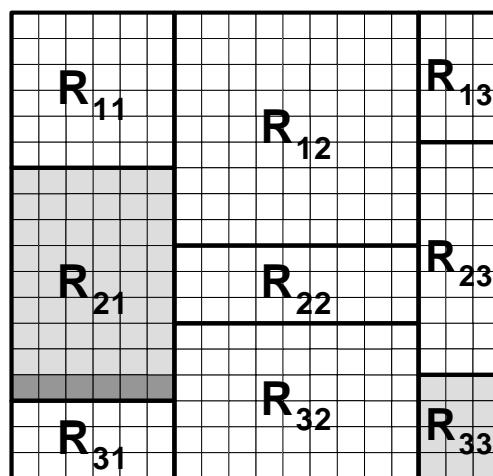

4.18 Different combinations of rectangles in a generalized block. (a) No  $\mathbf{s} \times \mathbf{s}$  block of rectangle  $R_{31}$  is a horizontal neighbor of rectangle  $R_{23}$ ; therefore,  $h[3][1][2][3] = 0$ . (b) All  $\mathbf{s} \times \mathbf{s}$  blocks of rectangle  $R_{31}$  are horizontal neighbors of rectangle  $R_{33}$ ;  $h[3][1][3][3] = 3$ . (c) Neighbors of rectangle  $R_{22}$  in rectangle  $R_{21}$  make up a  $3 \times 6$  rectangle area (shaded dark grey);  $h[2][1][2][2] = 3$ . (d) Neighbors of rectangle  $R_{33}$  in rectangle  $R_{21}$  make up the last row of this rectangle (shaded dark grey);  $h[2][1][3][3] = 1$ . ..... 233

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

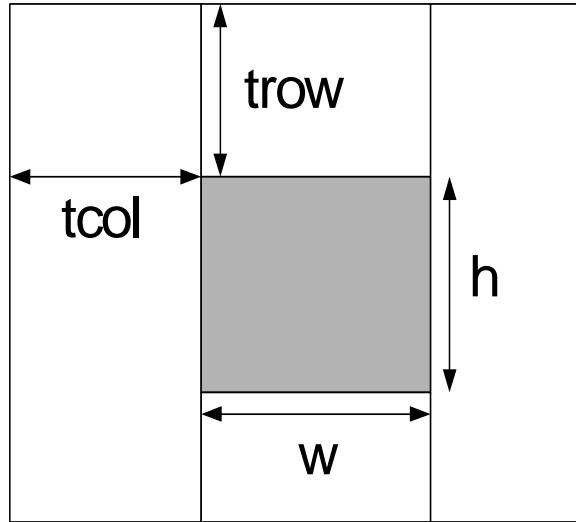

| 4.19 The parameter <b>w</b> gives the width of the rectangle of the generalized block assigned to different processors. The parameter <b>h</b> gives the height of rectangle of the generalized block assigned to different processors. The parameter <b>trow</b> gives the top leftmost point of the rectangle of the generalized block assigned to different processors from the first row of the generalized block. The parameter <b>tcol</b> gives the top leftmost point of the rectangle of the generalized block assigned to different processors from the first column of the generalized block. .... | 237 |

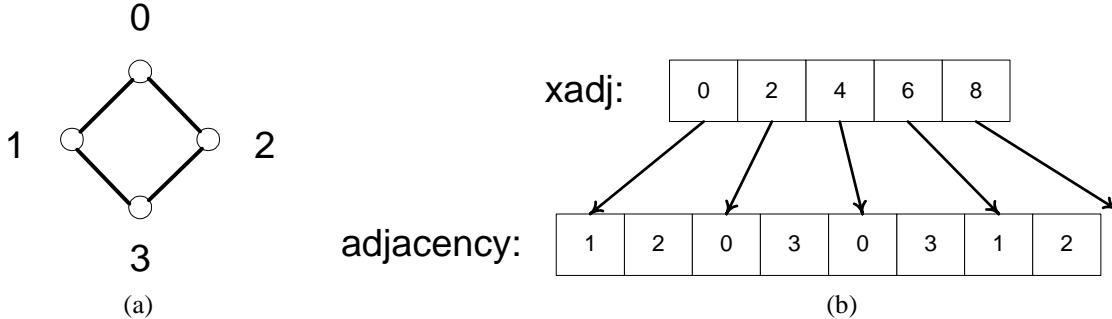

| 4.20 (a) A sample graph, and (b) The adjacency structure of the graph shown in (a). Adjacency structure for vertex 0 starts at 0 and the number of adjacent vertices are 2 given by $xadj[1] - xadj[0]$ . The adjacent vertices of vertex 0 are 1 and 2 given by $adjacency[0]$ and $adjacency[1]$ . Similarly adjacency structure for vertex 1 starts at 2 and the number of adjacent vertices are 2 given by $xadj[2] - xadj[1]$ . The adjacent vertices are 0 and 3 given by $adjacency[2]$ and $adjacency[3]$ . ....                                                                                      | 244 |

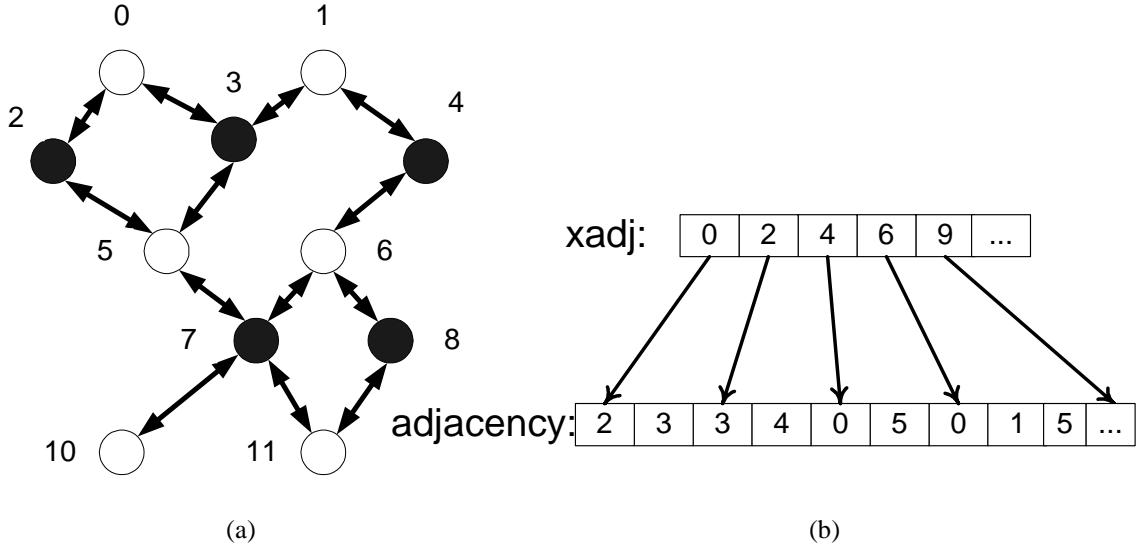

| 4.21 (a) A sample bipartite graph showing dependencies between black nodes and white nodes, and (b) The adjacency structure of the graph shown in (a). ....                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 246 |

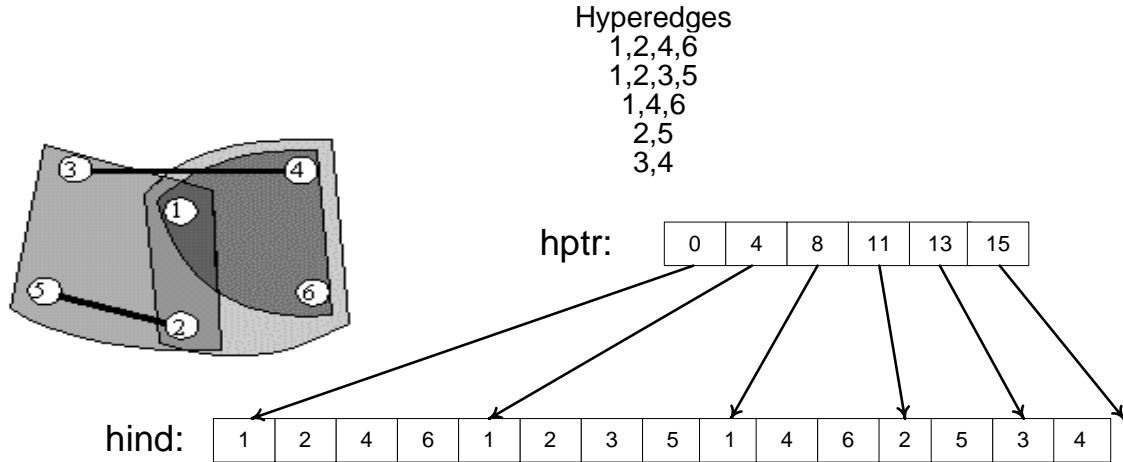

| 4.22 The <b>hptr</b> and <b>hind</b> arrays that are used to describe the hyperedges of the hypergraph. ....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 250 |

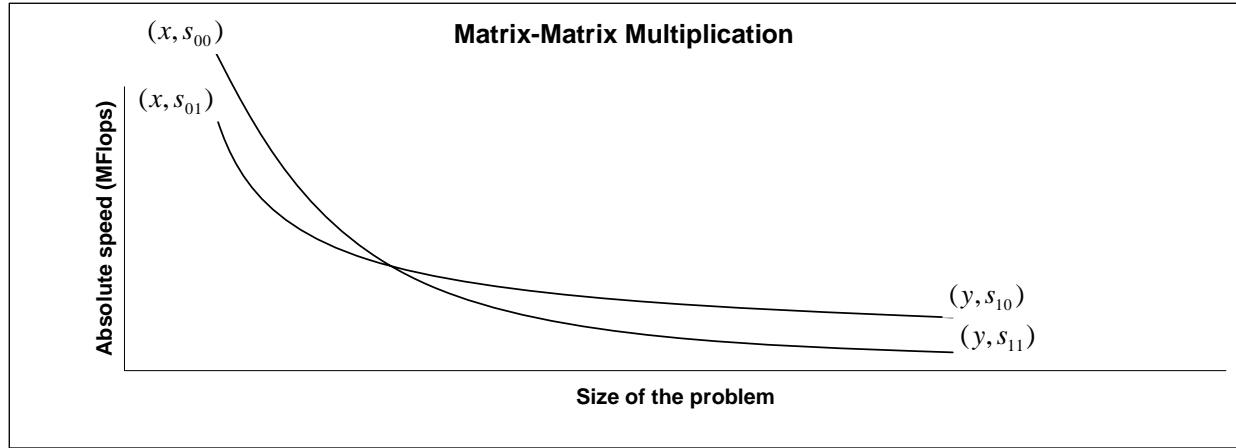

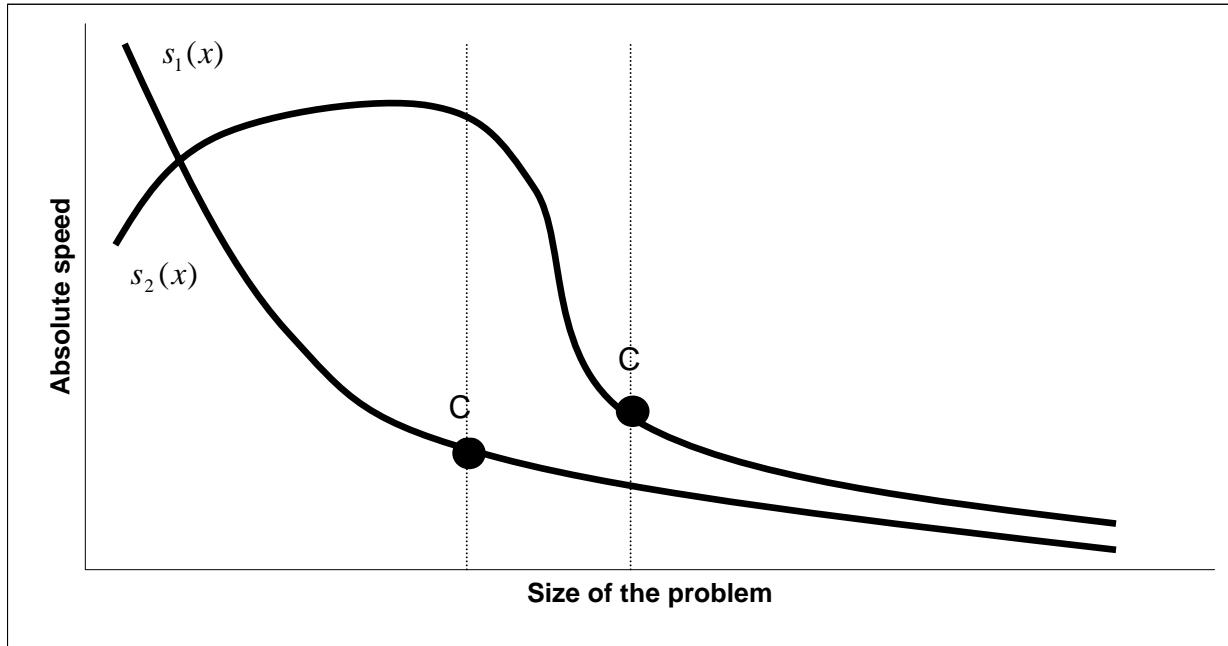

| 4.23 A small network of two processors whose speeds are shown against the size of the problem. The Matrix-Matrix Multiplication used here uses a poor solver that does not use memory hierarchy efficiently. ....                                                                                                                                                                                                                                                                                                                                                                                             | 256 |

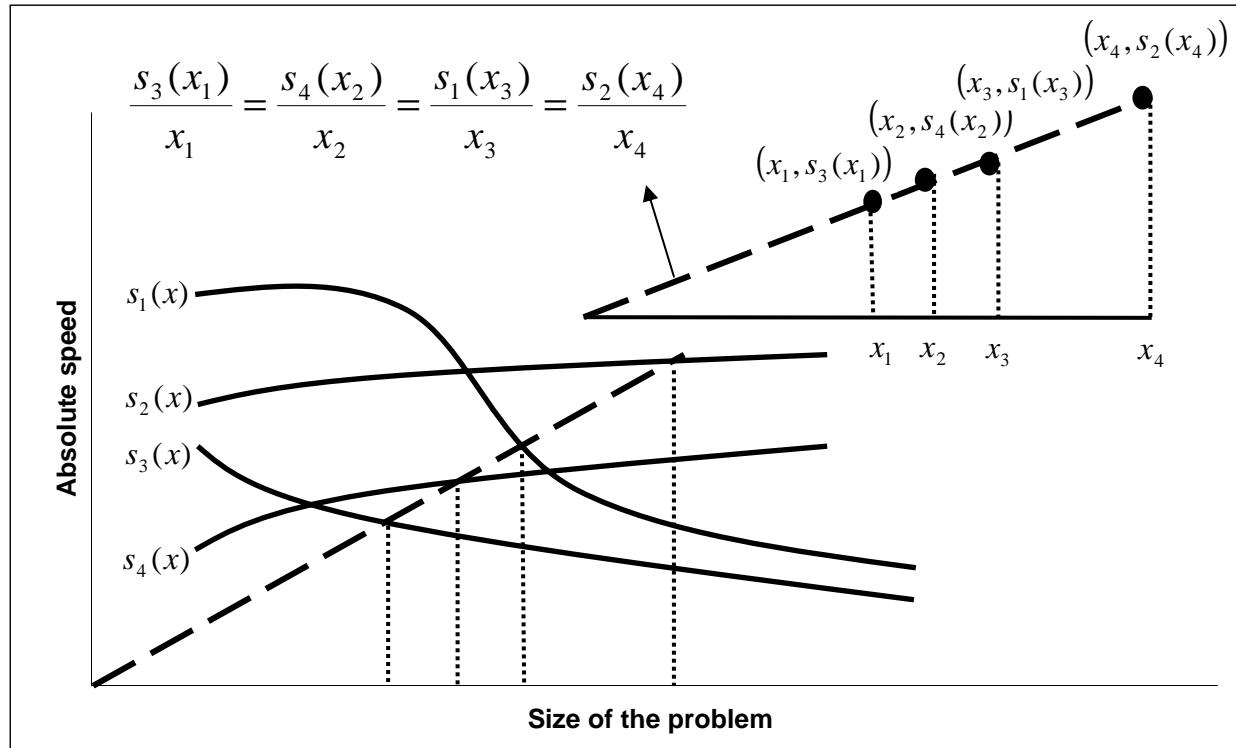

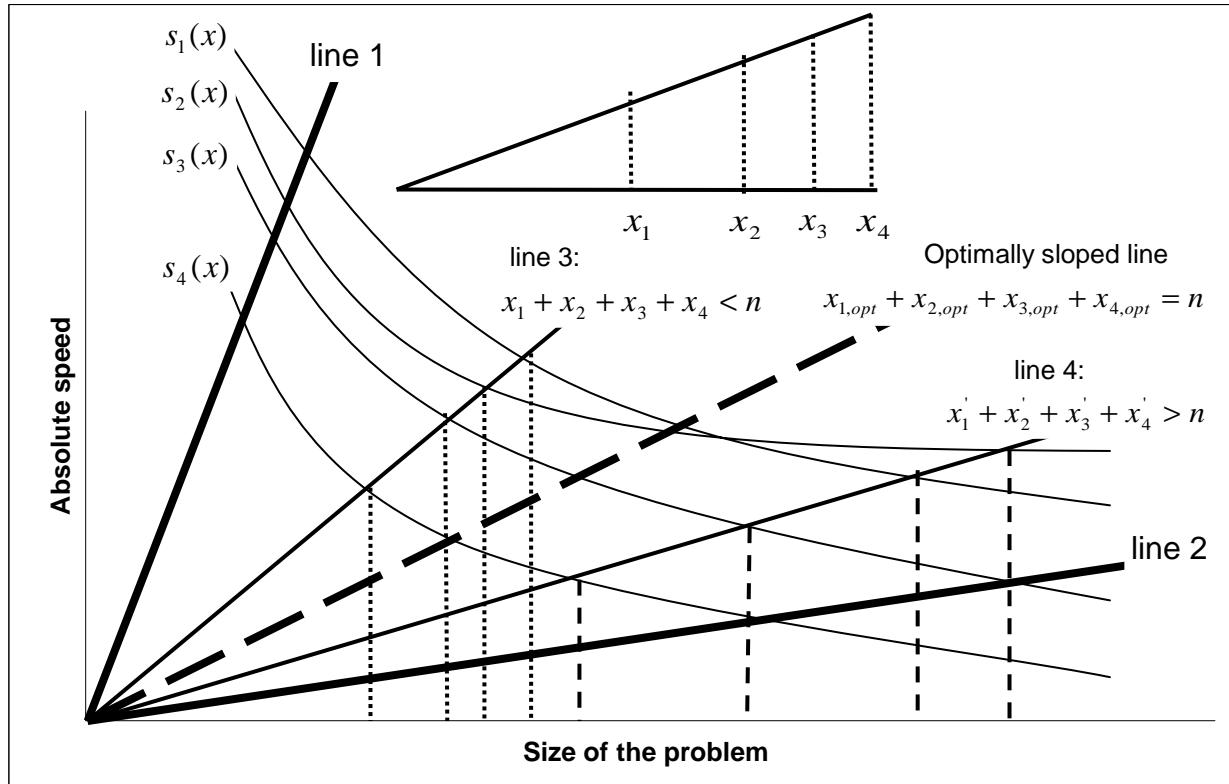

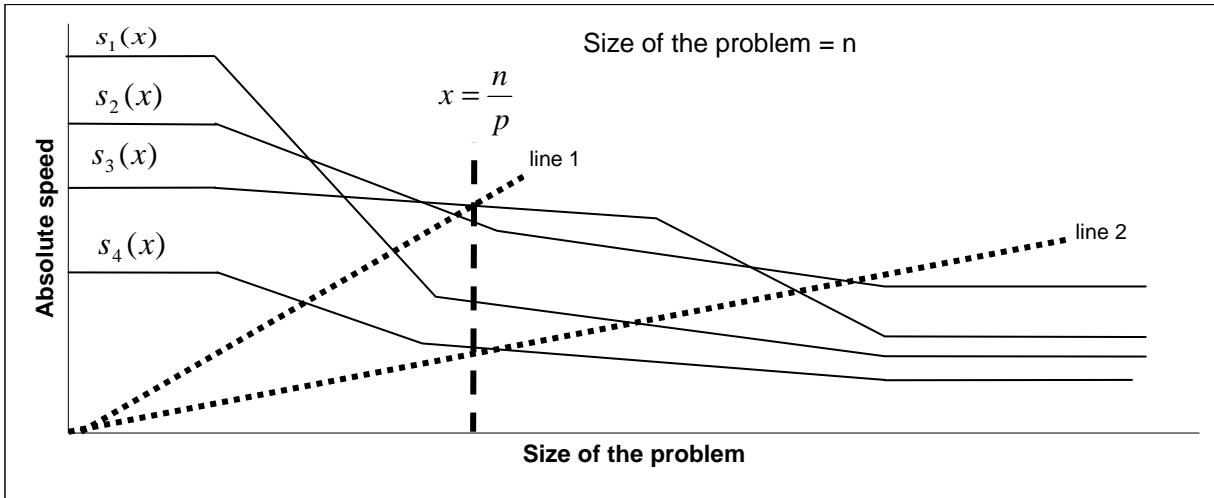

| 4.24 Optimal solution showing the geometric proportionality of the number of elements to the speed of the processor. $s_1(x)$ , $s_2(x)$ , $s_3(x)$ , and $s_4(x)$ are speeds of processors 1, 2, 3, and 4 respectively, which are functions of the size of the problem. ....                                                                                                                                                                                                                                                                                                                                 | 257 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

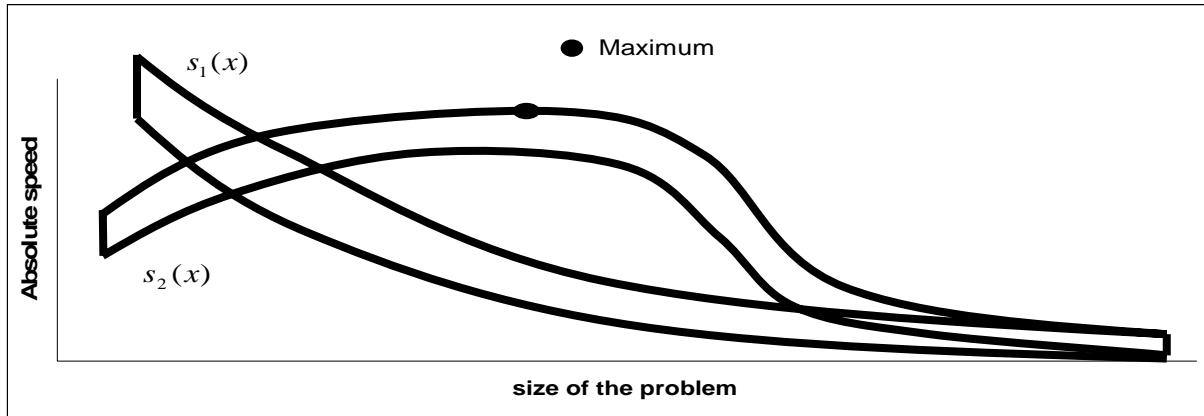

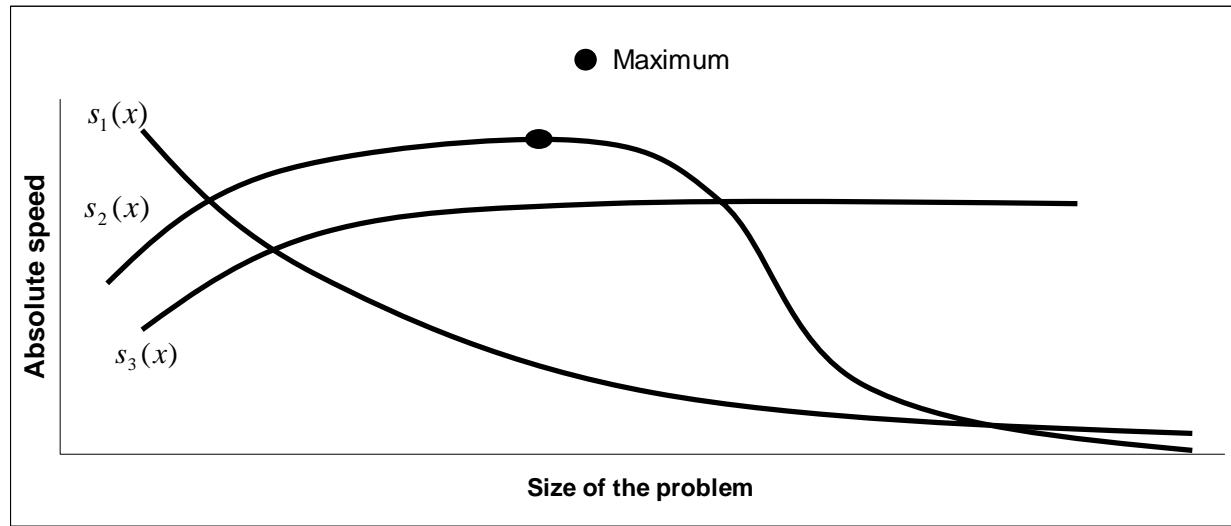

| 4.25 Typical shapes of the graphs representing the speed functions of the processors observed experimentally. The graph represented by $s_1(x)$ is strictly a decreasing function of the size of the problem. The graph represented by $s_2(x)$ is initially an increasing function of the size of the problem followed by a decreasing function of the size of the problem. The graph represented by $s_3(x)$ is strictly an increasing function of the size of the problem. | 258 |

| .....                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 258 |

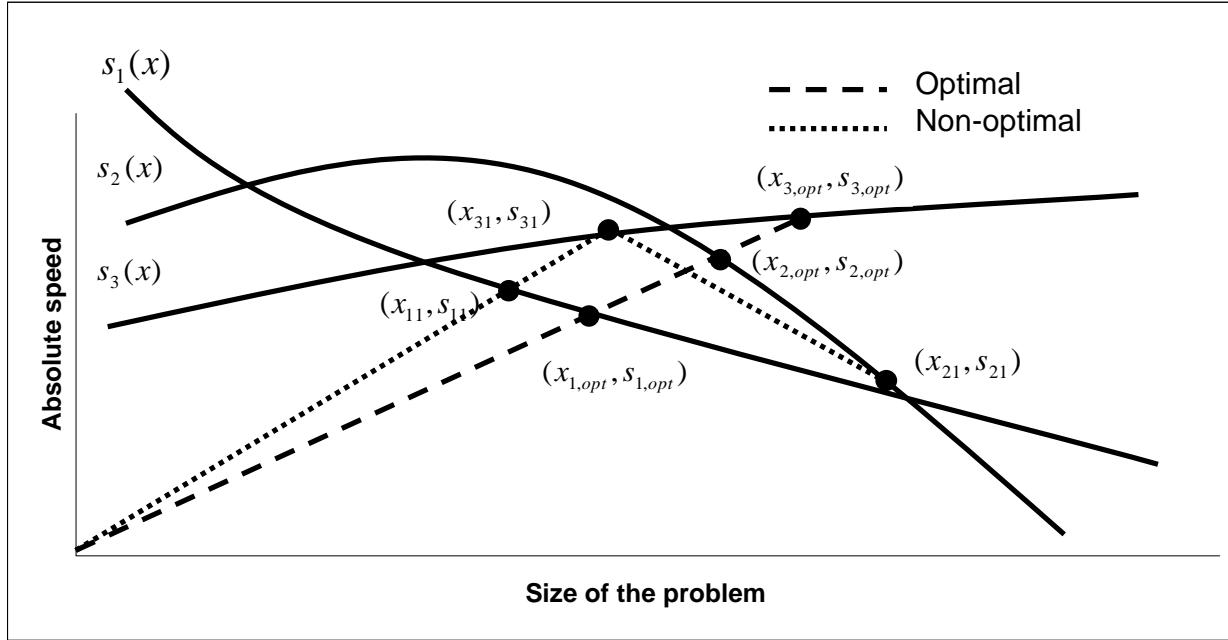

| 4.26 Uniqueness of the solution. The dashed line represents the optimal solution whereas the dotted line represents a non-optimal solution. ....                                                                                                                                                                                                                                                                                                                              | 260 |

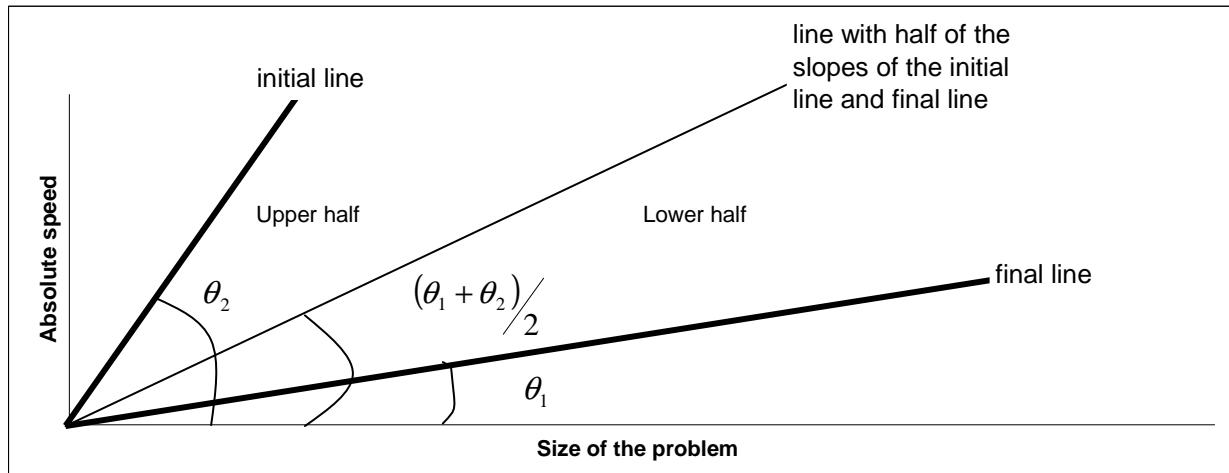

| 4.27 Determination of the slope of the line equal to half of the slopes of the initial and final lines. ....                                                                                                                                                                                                                                                                                                                                                                  | 262 |

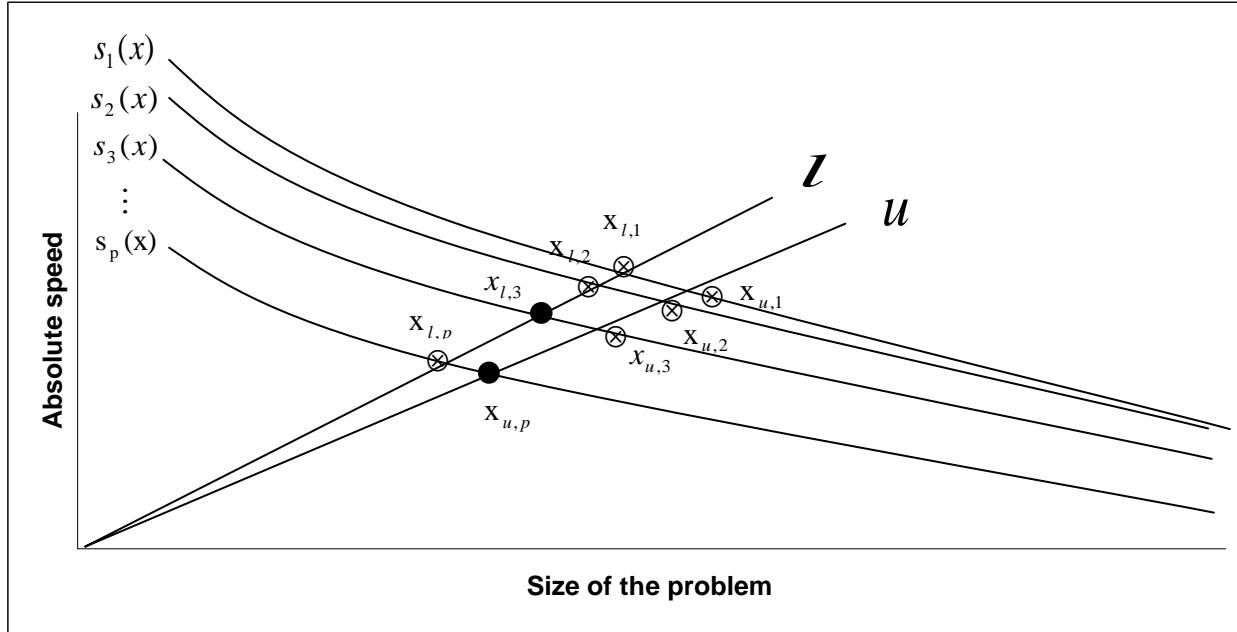

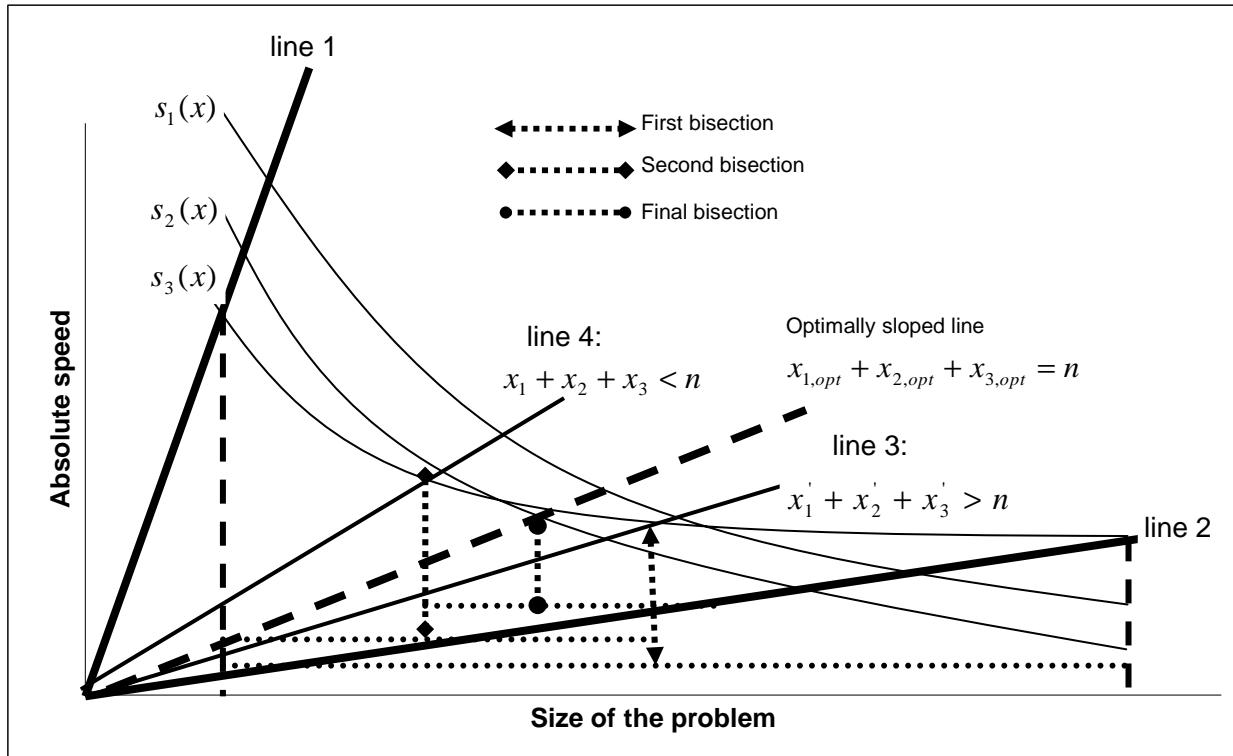

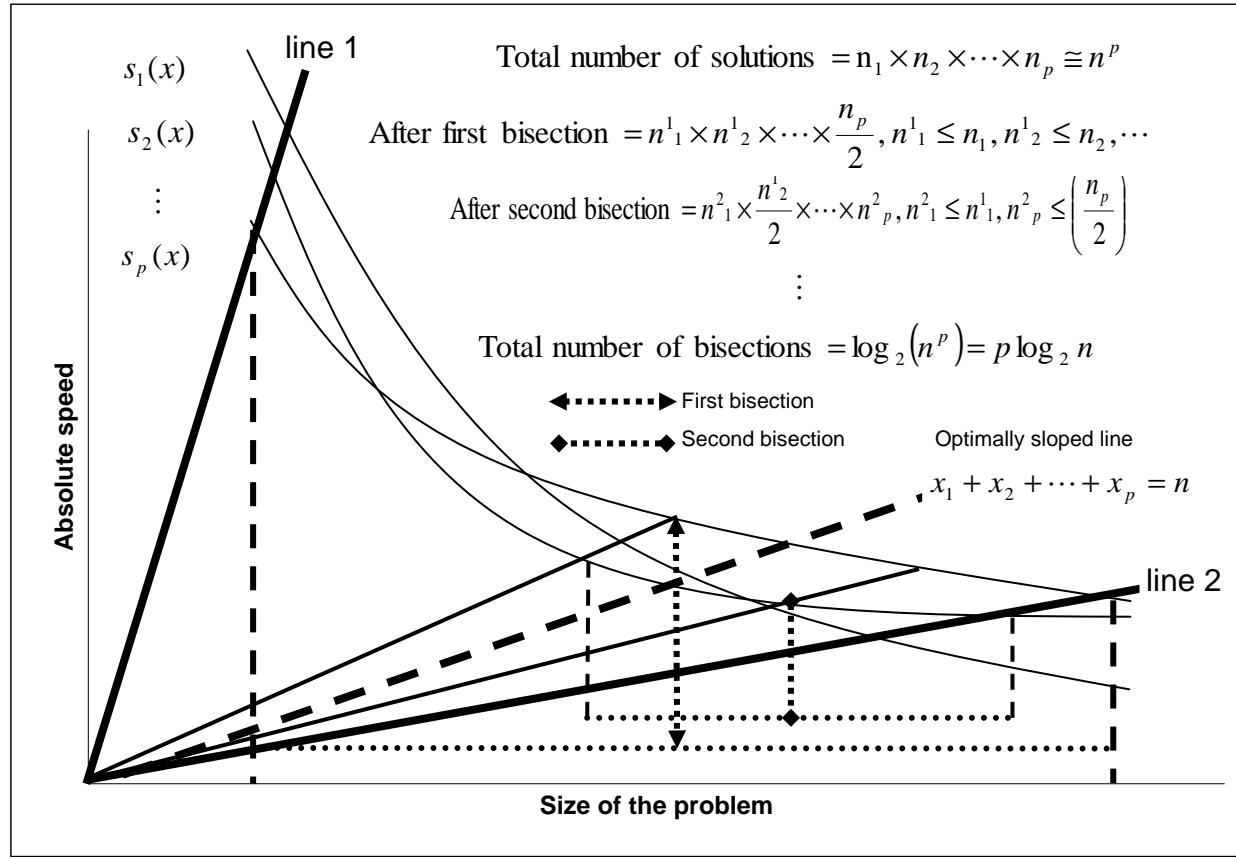

| 4.28 Use of bisection of the range to narrow down to the optimal solution satisfying the criterion that the number of elements should be proportional to the speed of the processor. $n$ is the size of the problem. ....                                                                                                                                                                                                                                                     | 263 |

| 4.29 Fine tuning procedure chooses the final $p$ points of intersection from the $p$ integer points closest to the non-integer points on line $l$ and $p$ integer points closest to the non-integer points on line $u$ . There are no integers between the lines $l$ and $u$ . The integers closest to the non-integer points on lines $l$ and $u$ are indicated by crossed dots whereas integer points lying on lines $l$ and $u$ are indicated by dark dots. ....           | 264 |

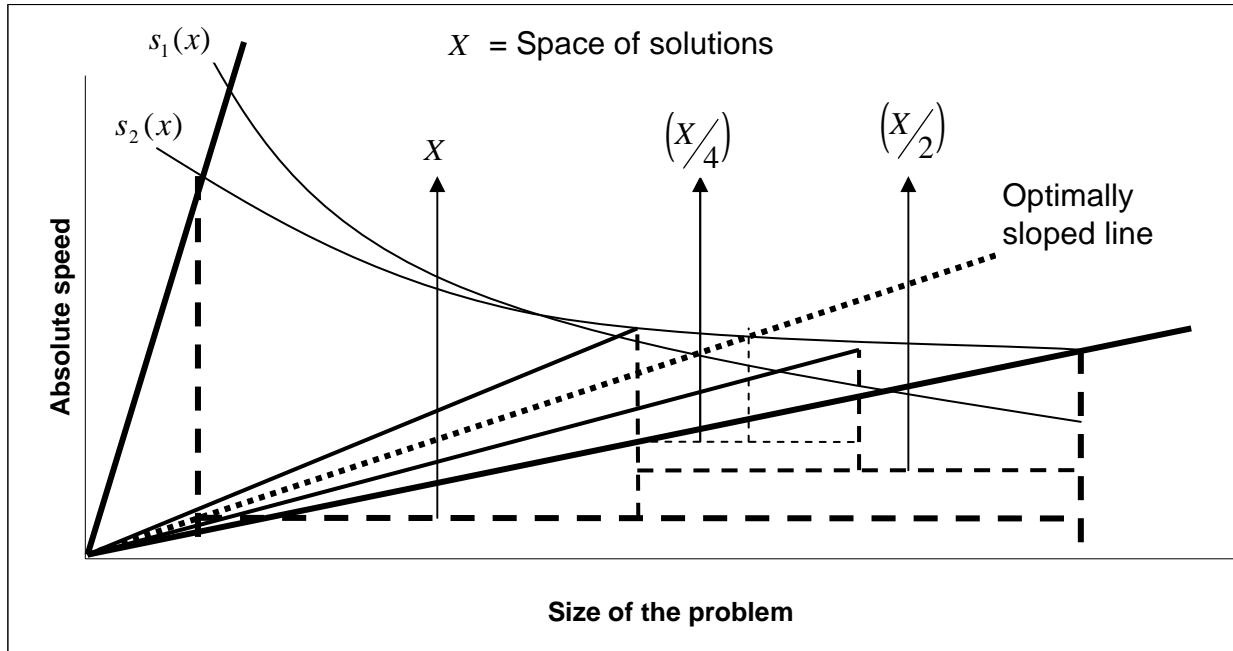

| 4.30 Bisection of the space of solutions in the modified algorithm. ....                                                                                                                                                                                                                                                                                                                                                                                                      | 266 |

| 4.31 Modification of the algorithm shown in Figure 4.28 where the bisection results in efficient solution. $n$ is the size of the problem. ....                                                                                                                                                                                                                                                                                                                               | 266 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.32 | Schematic proof of the complexity of the modified algorithm. The total number of bisections is $p \times \log_2 n$ . At each step of bisection, $p$ intersection points are obtained giving a total complexity of $O(p^2 \times \log_2 n)$ .                                                                                                                                                                                                                                                                                                                          | 268 |

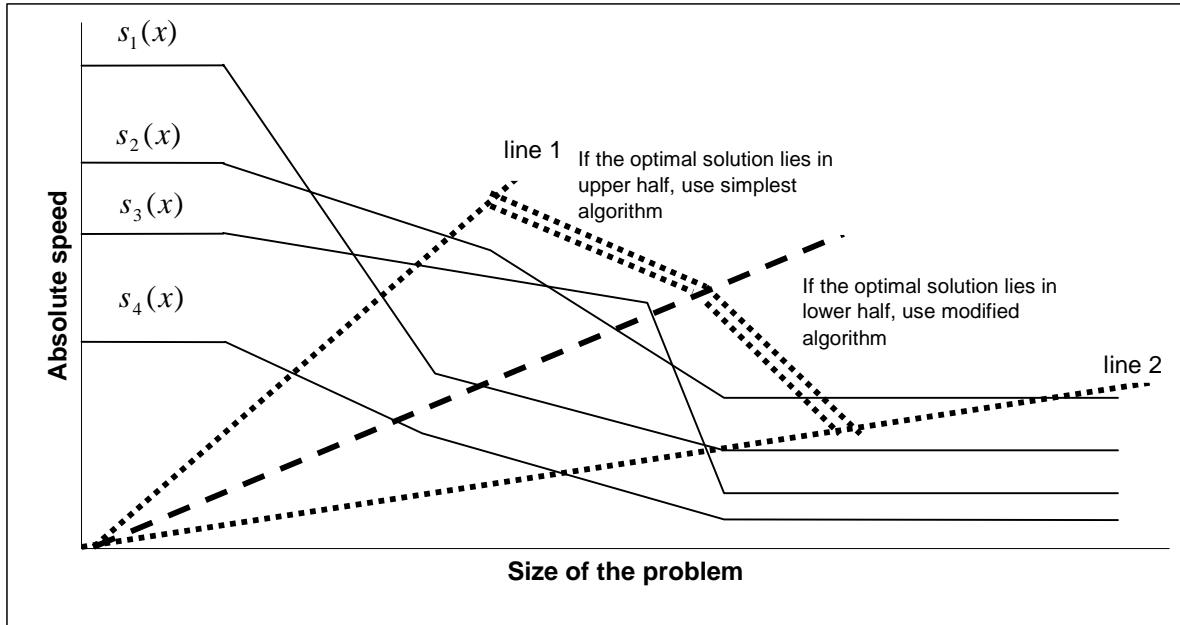

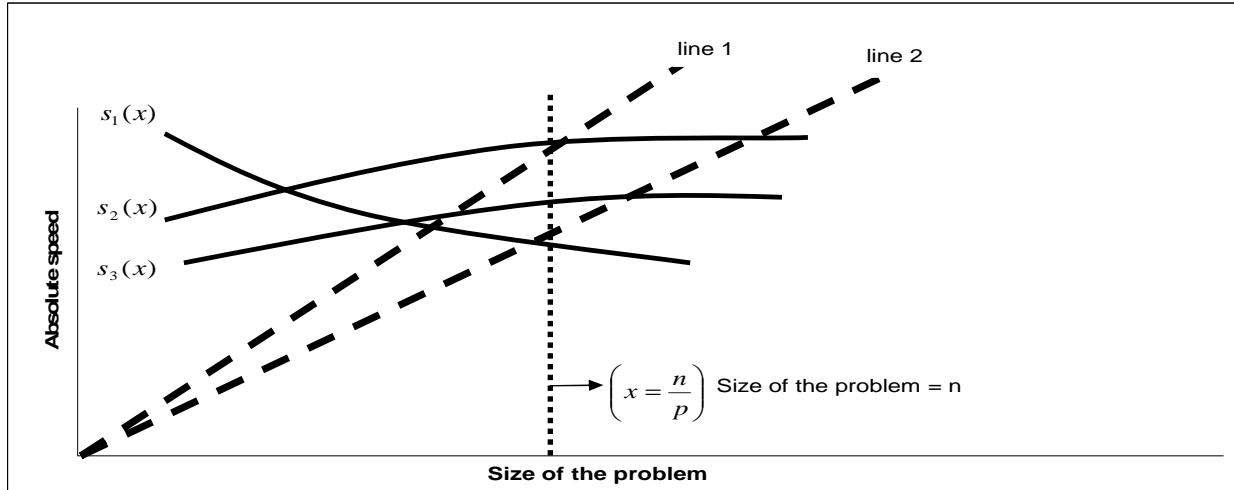

| 4.33 | For most real-life situations, the optimal solution lies in the region with polynomial slopes. The optimal solution lies between <b>line1</b> and <b>line2</b> and they enclose a region with all polynomial slopes.                                                                                                                                                                                                                                                                                                                                                  | 269 |

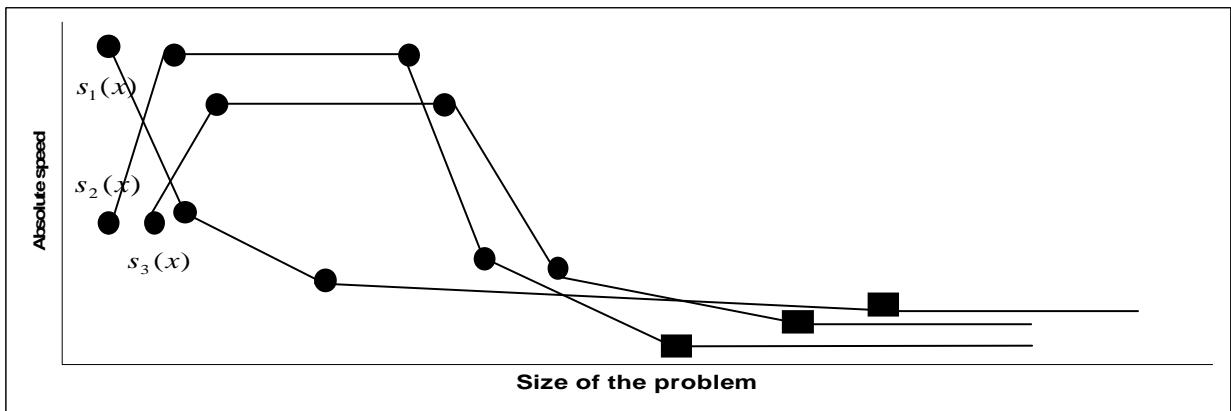

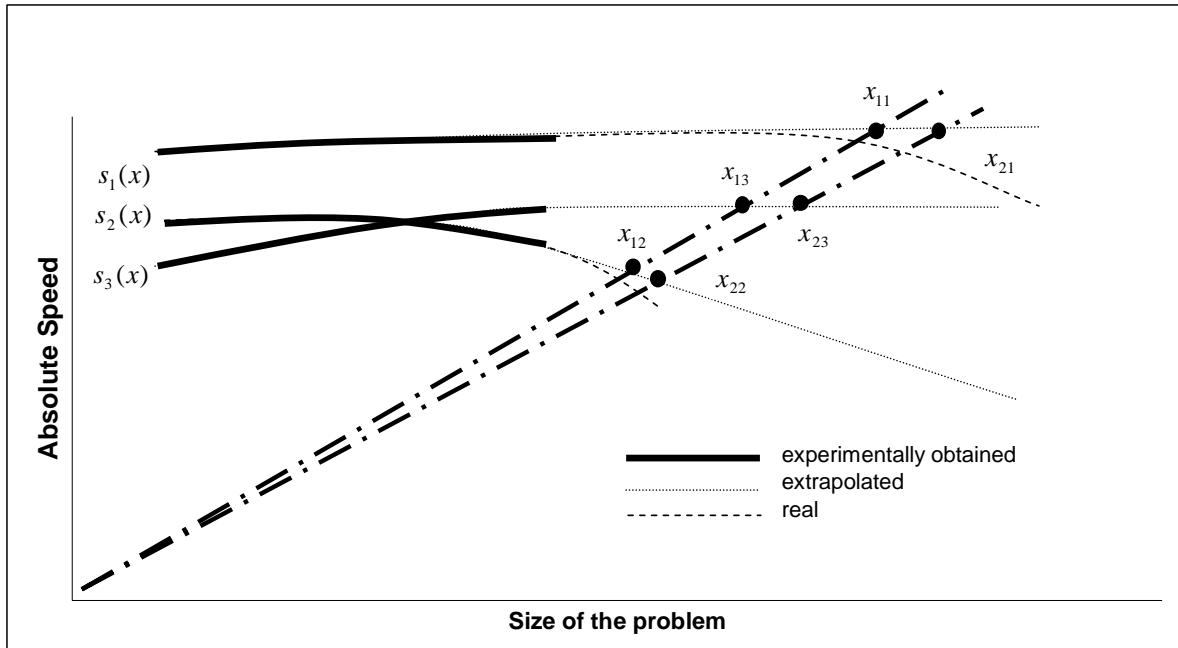

| 4.34 | Using piecewise linear approximation to build speed functions for 3 processors. The circular points are experimentally obtained whereas the square points are calculated using heuristics but not experimentally obtained. The speed function for processor $s_1(x)$ is built from 3 experimentally obtained points (application run on this processor uses memory hierarchy inefficiently) whereas the speed functions $s_2(x)$ and $s_3(x)$ (application run on these processors use memory hierarchy efficiently) are built from 4 experimentally obtained points. | 269 |

| 4.35 | Using a combination of simplest and modified algorithm to efficiently solve problems for real-life applications.                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 271 |

| 4.36 | Illustration of the regions where our data partitioning algorithms are better compared to out-of-core algorithms and vice versa. C is the crossover point at which out-of-core algorithms start performing better than our data partitioning algorithms.                                                                                                                                                                                                                                                                                                              | 272 |

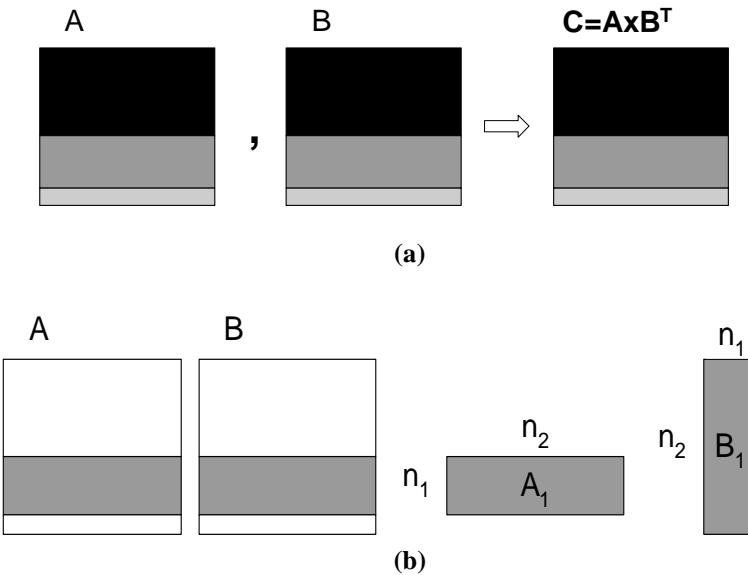

| 4.37 | (a) Matrix operation $C = A \times B^T$ with matrices A, B, and C. Matrices A, B, and C are horizontally sliced. The number of elements in each slice is proportional to the speed of the processor. (b) Serial matrix multiplication $A_1 \times B_1$ ( $B_1 = B^T$ ) of two dense non-square matrices of sizes $n_1 \times n_2$ and $n_2 \times n_1$ respectively to estimate the absolute speed of processor                                                                                                                                                       |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1. The parameter $n_2$ is fixed during the application of the set partitioning algorithm and is equal to $\mathbf{n}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 275 |

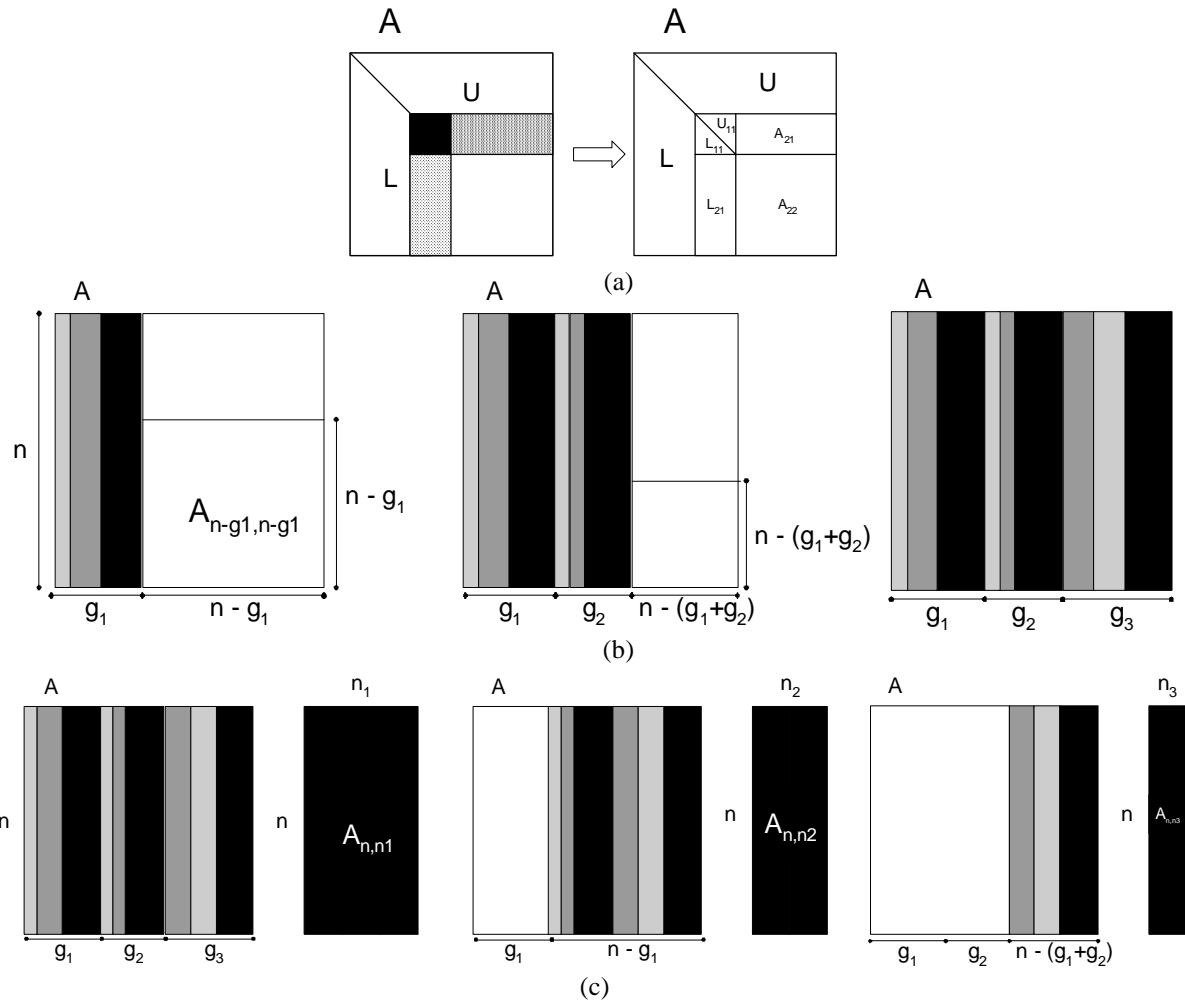

| 4.38 (a) One step of the LU factorization algorithm of a dense square matrix $A$ of size $\mathbf{n} \times \mathbf{n}$ . (b) The matrix $A$ is partitioned using Variable Group Block distribution. This figure illustrates the distribution for $\mathbf{n}=576, \mathbf{b}=32, \mathbf{p}=3$ . The distribution inside groups $G_1, G_2$ , and $G_3$ are $\{2,1,1,0,0,0\}$ , $\{2,1,0,0,0\}$ , and $\{2,2,1,1,0,0,0\}$ . (b) Serial LU factorization of a dense non-square matrix is used to estimate the absolute speed of a processor. Since the Variable Group Block distribution uses the functional model where absolute speed of the processor is represented by a function of a size of the problem, the distribution uses absolute speeds at each step of the LU decomposition that are based on the size of the problem solved at that step. As seen in this figure, at each of the steps for processor 0, the functional dependence of the absolute speed on the problem size gives the speeds based on solving the problem size at that step, which is equal to the number of elements in matrices $A_{n,n_1}$ , $A_{n,n_2}$ , and $A_{n,n_3}$ respectively. That is at each of the steps for processor 0, the absolute speeds are based on serial LU decomposition of matrices $A_{n,n_1}$ , $A_{n,n_2}$ , and $A_{n,n_3}$ . | 278 |

| 4.39 Detection of the initial two lines between which the solution lies.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 283 |

| 4.40 The cost of finding the optimal solution using the partitioning algorithm. $\mathbf{p}$ is the number of processors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 284 |

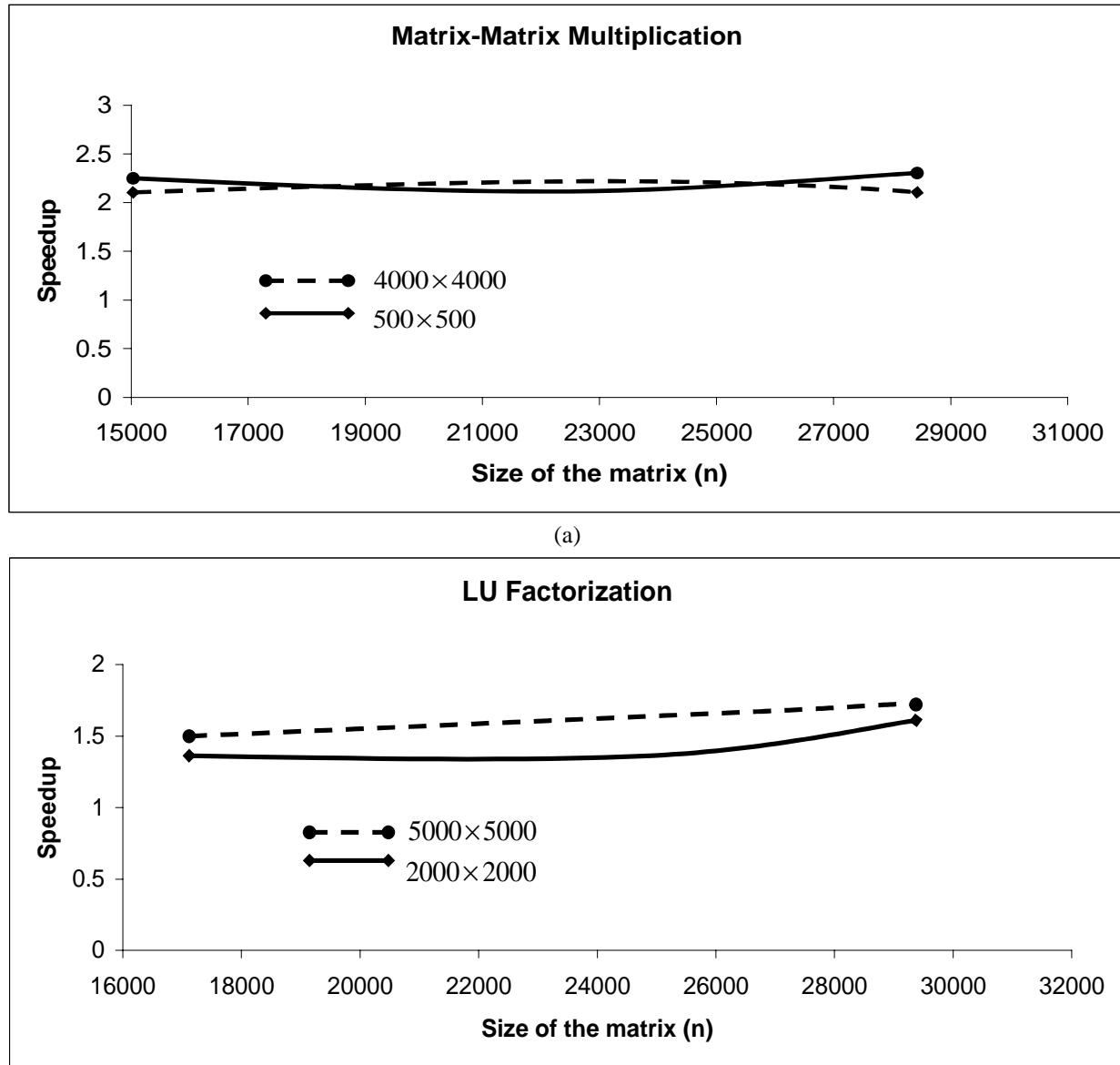

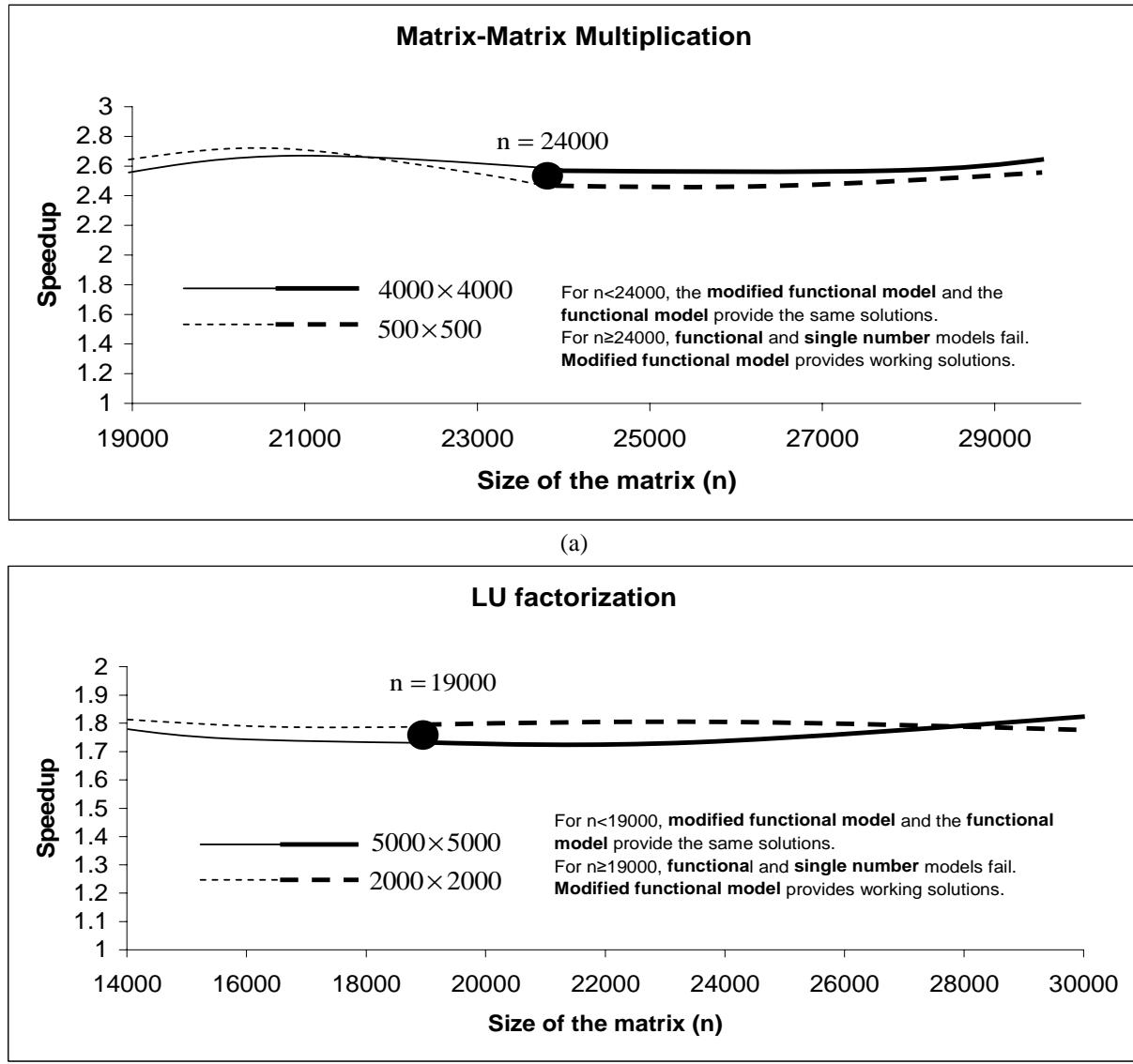

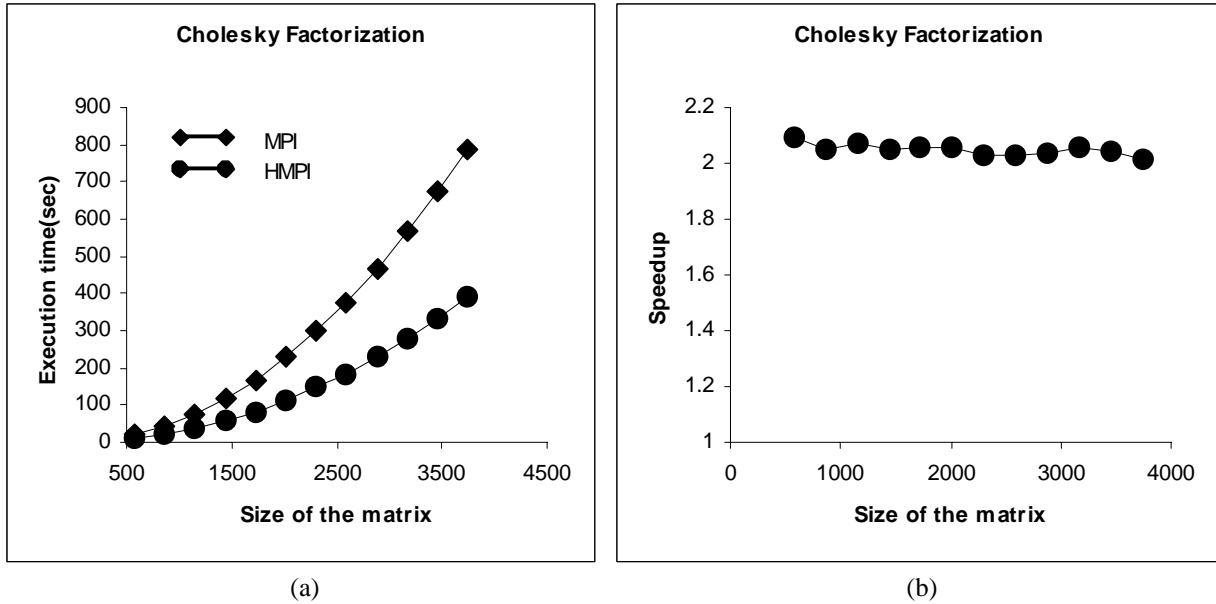

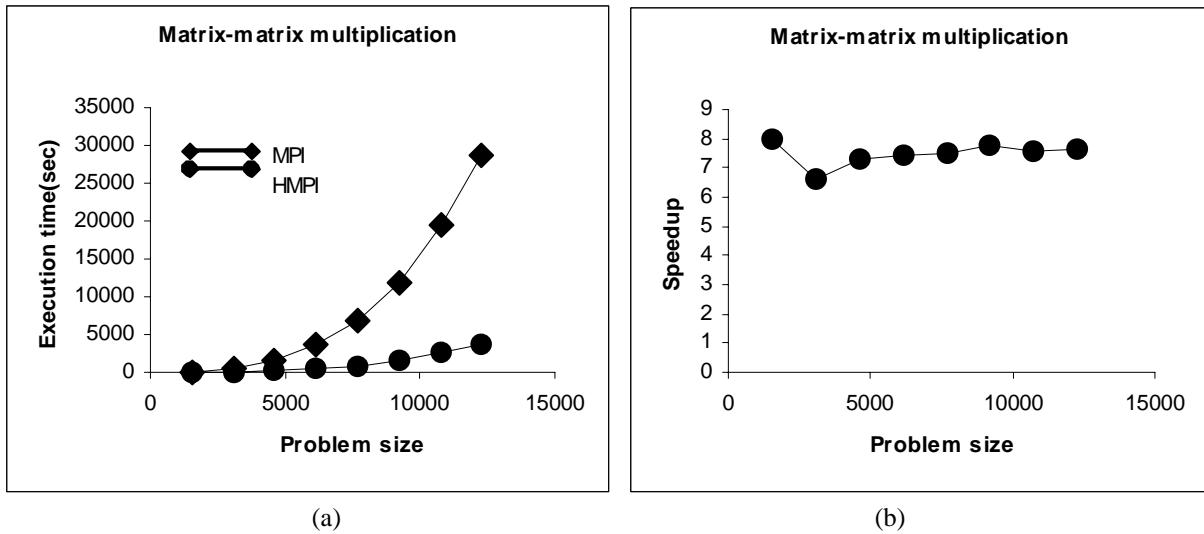

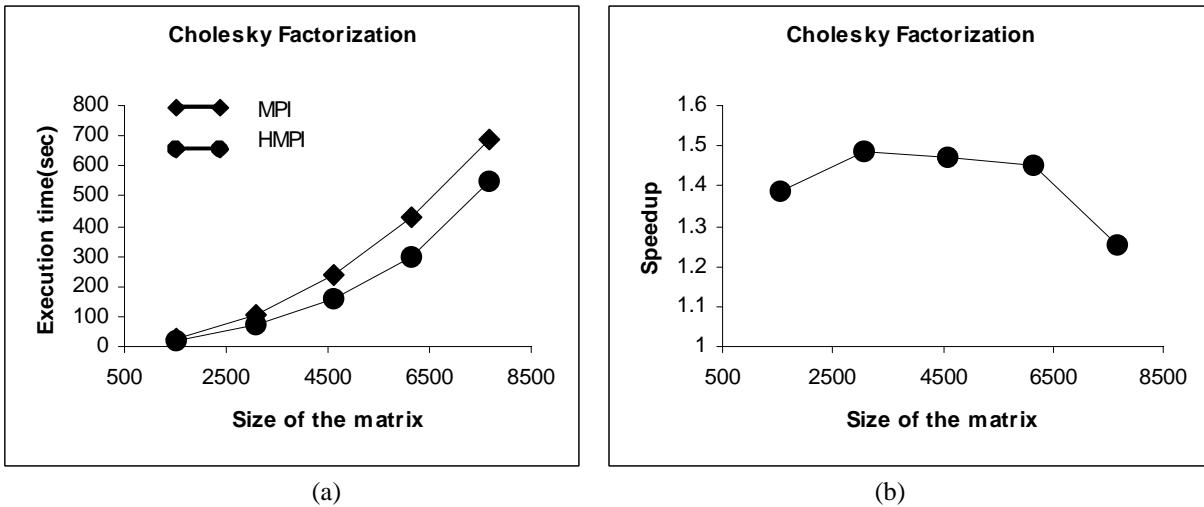

| 4.41 Results obtained using the network of heterogeneous computers shown in Table 4.8. The speedup calculated is the ratio of the execution time of the application using the single number model over the execution time of the application using the functional model. (a) Comparison of speedups of matrix-matrix multiplication. For the single number model,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

the speeds are obtained using serial matrix-matrix multiplication of two dense square matrices. For the solid lined curve, the matrices used are of size  $500 \times 500$ . For the dashed curve, the matrices used are of size  $4000 \times 4000$ . (b) Comparison of speedups of LU factorization. For the single number model, the speeds are obtained using serial LU factorization of a dense square matrix. For the solid lined curve, the matrix used is of size  $2000 \times 2000$ . For the dashed curve, the matrix used is of size  $5000 \times 5000$ . ..... 285

4.42 The effect of caching and paging in reducing the execution speed of each of the four applications run on network of heterogeneous computers shown in Table 4.11. (a) ArrayOpsF, (b) TreeTraverse, (c) MatrixMultATLAS, and (d) MatrixMult. P is the point where paging starts occurring. ..... 289

4.43 A small network of three processors whose speeds are shown against the size of the problem. The dotted lines passing through the origin represent solutions provided by the functional model. The bold curves represent the experimentally obtained speed functions. The dotted curves represent reasonable approximations of the speed functions in a continuous manner. The dashed curves represent the real behavior of the speed functions. The first dotted line giving the data distribution  $(x_{11}, x_{12}, x_{13})$  is a non-optimal solution. The second dotted line giving the data distribution  $(x_{21}, x_{22}, x_{23})$  is not a solution at all. ..... 291

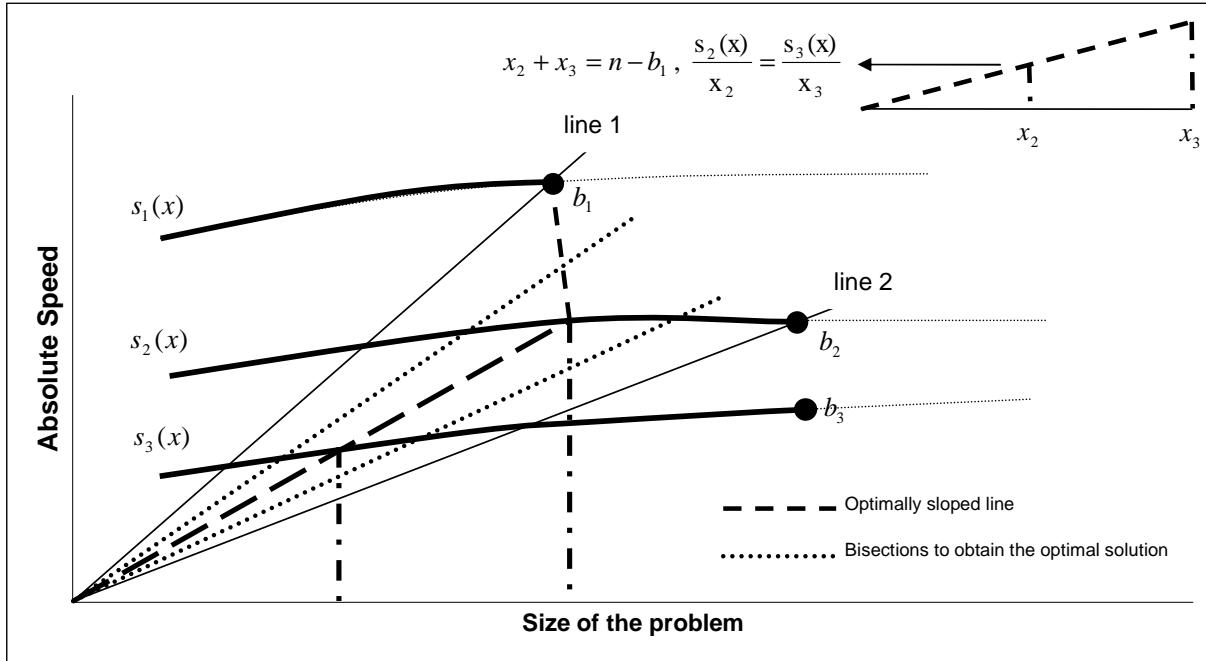

4.44 The partitioning algorithm for the problem size  $\mathbf{n}$ . The bold curves represent the experimentally obtained speed functions. The dotted curves represent reasonable approximations of the speed functions in a continuous manner. For processor represented by speed function  $s_1(x)$ , we assign this processor the number of elements equal to its upper bound  $\mathbf{b}_1$ . We then partition the set with remaining  $\mathbf{n}-\mathbf{b}_1$  elements amongst the

processors represented by speed functions  $s_2(x)$  and  $s_3(x)$  respectively. The region between the lines **line1** and **line2** is bisected to narrow down to the optimal solution.

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| ..... | 297                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

| 4.45  | Operating system tools to determine the user-available memory for an application. The user-available memory is highlighted in bold. .....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 302 |

| 4.46  | Using piece-wise linear approximation to build speed functions for 3 processors. The circular points are experimentally obtained whereas the square points represent the upper bounds. The speed function for processor $s_1(x)$ is built from 3 experimentally obtained points (application run on this processor uses memory hierarchy inefficiently) whereas the speed functions $s_2(x)$ and $s_3(x)$ (application run on these processors use memory hierarchy efficiently) are built from 4 experimentally obtained points. Speeds of the processors are assumed to be zero for problem sizes beyond their upper bounds. ....                                                                                                                                                                                                                                                                                                     | 305 |

| 4.47  | Results obtained using the network of heterogeneous computers shown in Table 4.12. The speedup calculated is the ratio of the execution time of the application using a single number model over the execution time of the application using a functional model. (a) Comparison of speedups of matrix-matrix multiplication. For the single number models, the speeds are obtained using serial matrix-matrix multiplication of two dense square matrices. For the solid lined curves, the matrices used are of size $4000 \times 4000$ . For the dashed curves, the matrices used are of size $500 \times 500$ . (b) Comparison of speedups of LU factorization. For the single number models, the speeds are obtained using serial LU factorization of a dense square matrix. For the solid lined curves, the matrix used is of size $5000 \times 5000$ . For the dashed curves, the matrix used is of size $2000 \times 2000$ . .... | 307 |

|     |                                                                                                                                                                                                                                                                                                          |     |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

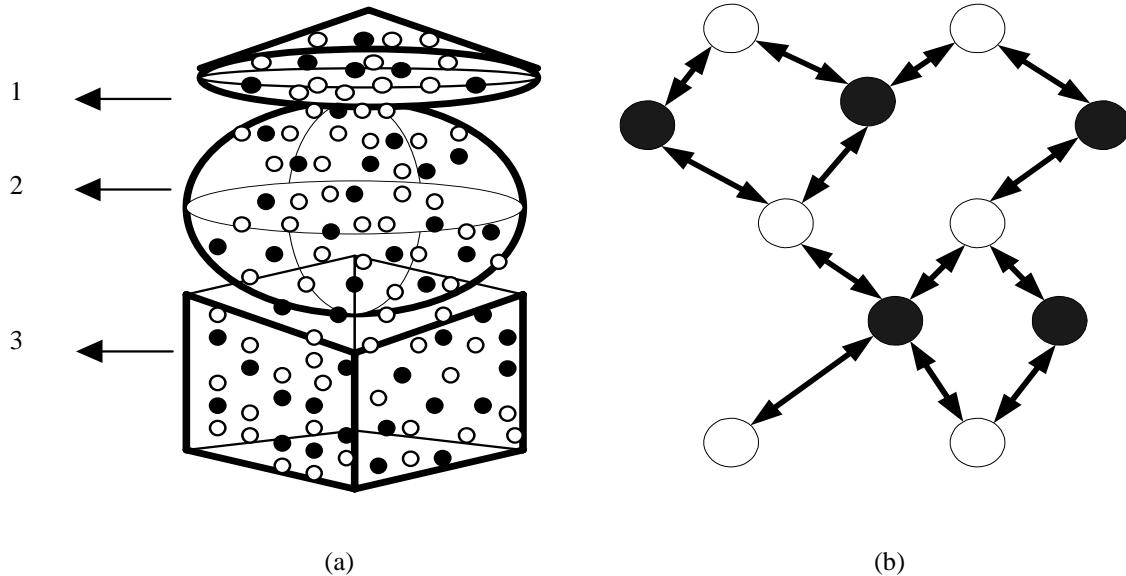

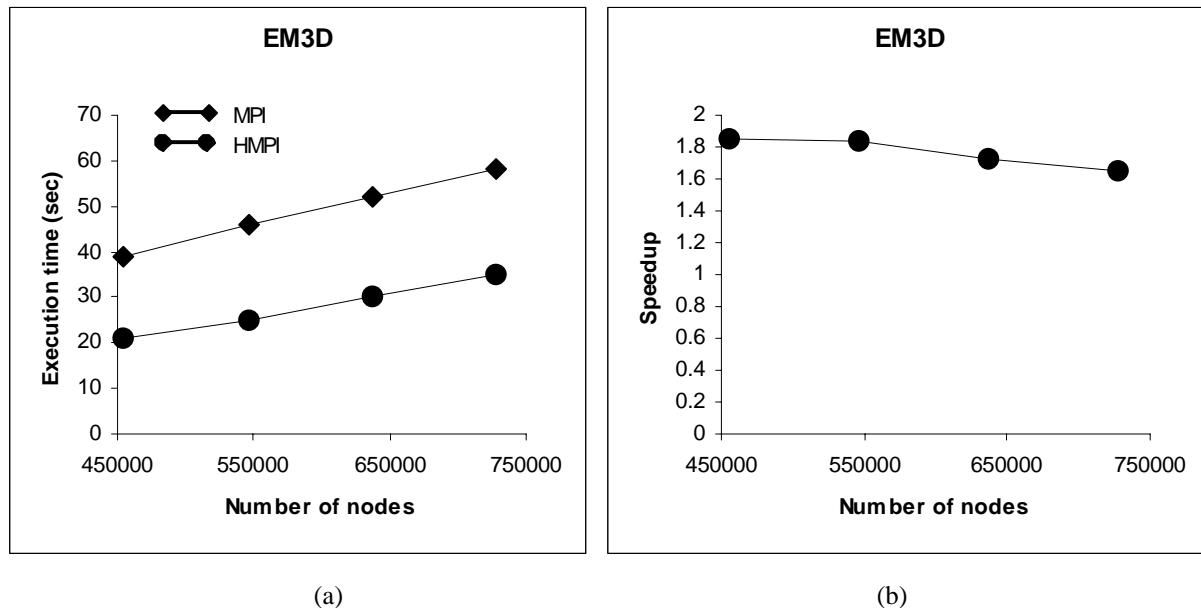

| 5.1 | (a) A sample three dimensional object consists of three subbodies. In each subbody, the electric field value is represented as a white dot, an E node, and the magnetic field value represented by a black dot, an H node and (b) A bipartite graph showing the dependencies between E and H nodes. .... | 316 |

| 5.2 | The most relevant fragments of code of the MPI program implementing the EM3D algorithm. ....                                                                                                                                                                                                             | 317 |

| 5.3 | Specification of the performance model of the EM3D algorithm in the HMPI's performance definition language. ....                                                                                                                                                                                         | 318 |

| 5.4 | The most relevant code fragments of the HMPI program implementing the algorithm of EM3D. ....                                                                                                                                                                                                            | 320 |

| 5.5 | Example of two-step distribution of a $6 \times 6$ generalized block over a $3 \times 3$ processor grid.                                                                                                                                                                                                 |     |

The relative speed of processors is given by matrix  $s = \begin{pmatrix} 0.11 & 0.25 & 0.05 \\ 0.17 & 0.09 & 0.08 \\ 0.05 & 0.17 & 0.03 \end{pmatrix}$ . (a) At the